## Ph.D. DEGREE IN Electronic and Computer Engineering

Cycle XXXV

# **Optimizing Neural Networks for Embedded Edge-Processing Platforms.**

ING-INF/01

Ph.D. Student:

Paola Busia

Supervisor

Prof. Paolo Meloni

Final exam. Academic Year 2021/2022 Thesis defence: February 2023 Session

To my Family,

# Contents

| 1 | Intro                    | itroduction |                                                     |    |  |  |

|---|--------------------------|-------------|-----------------------------------------------------|----|--|--|

| 2 | State                    | e of the    | Art                                                 | 7  |  |  |

|   | 2.1                      | Edge-p      | processing Platforms                                | 8  |  |  |

|   | 2.2                      | CNN n       | nodel optimization                                  | 9  |  |  |

|   |                          | 2.2.1       | Network compression                                 | 9  |  |  |

|   |                          | 2.2.2       | Hardware-Aware Neural Architecture Search           | 10 |  |  |

|   |                          | 2.2.3       | Hardware cost modeling                              | 12 |  |  |

|   |                          | 2.2.4       | Neural Architecture Search for KWS                  | 15 |  |  |

|   | 2.3                      | Emerg       | ing Neural Networks                                 | 17 |  |  |

| 3 | Opti                     | mizing      | the design space exploration: the ALOHA design flow | 19 |  |  |

|   | 3.1                      | ALOH        | A CNN design flow                                   | 23 |  |  |

|   |                          | 3.1.1       | Dataset Management Utility                          | 23 |  |  |

|   |                          | 3.1.2       | Selection Procedure                                 | 24 |  |  |

|   |                          | 3.1.3       | Evaluation tools                                    | 25 |  |  |

|   |                          | 3.1.4       | Deployment                                          | 27 |  |  |

|   | 3.2                      | CNN s       | election procedure implementation                   | 27 |  |  |

|   |                          | 3.2.1       | Fast implementation                                 | 27 |  |  |

|   |                          | 3.2.2       | Accurate Implementation                             | 30 |  |  |

|   |                          | 3.2.3       | Selection time                                      | 31 |  |  |

|   | 3.3 Experimental Results |             |                                                     |    |  |  |

|   |                          | 3.3.1       | Search Space definition                             | 33 |  |  |

|   |     | 3.3.2    | Preliminary Pre-processing exploration         | 34 |

|---|-----|----------|------------------------------------------------|----|

|   |     | 3.3.3    | Use-case 1                                     | 35 |

|   |     | 3.3.4    | Use-case 2                                     | 38 |

|   |     | 3.3.5    | Selection's quality assessment.                | 42 |

|   |     | 3.3.6    | Closing remarks.                               | 42 |

| 4 | Har | dware-   | aware performance estimation: the ALOHA method | 45 |

|   | 4.1 | Backg    | round                                          | 47 |

|   |     | 4.1.1    | The computational tensor of a CNN layer.       | 47 |

|   |     | 4.1.2    | OPS-based Performance prediction               | 49 |

|   |     | 4.1.3    | Roofline Model                                 | 50 |

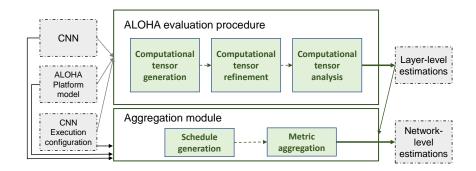

|   | 4.2 | ALOH     | A estimation method                            | 51 |

|   | 4.3 | ALOH     | IA platform Model                              | 52 |

|   | 4.4 | ALOH     | A evaluation Procedure                         | 58 |

|   |     | 4.4.1    | Computational tensor generation                | 59 |

|   |     | 4.4.2    | Computational tensor refinement                | 60 |

|   |     | 4.4.3    | Computational tensor analysis                  | 62 |

|   | 4.5 | CNN r    | metric aggregation                             | 64 |

|   | 4.6 | Experi   | imental Results                                | 67 |

|   |     | 4.6.1    | Layer-level accuracy                           | 67 |

|   |     | 4.6.2    | Impact on energy consumption estimation        | 70 |

|   |     | 4.6.3    | Impact on NAS                                  | 71 |

|   |     | 4.6.4    | Impact of aggregation on prediction accuracy   | 77 |

|   |     | 4.6.5    | Closing remarks                                | 81 |

| 5 | Eme | erging l | Neural Networks: Optimal Transformer Design    | 83 |

|   | 5.1 | Proble   | em definition                                  | 84 |

|   | 5.2 | Detect   | tor                                            | 86 |

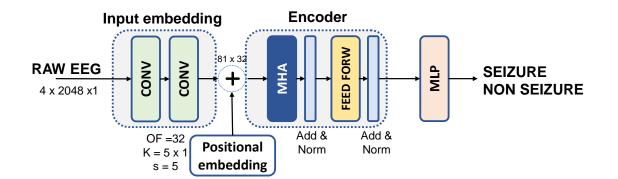

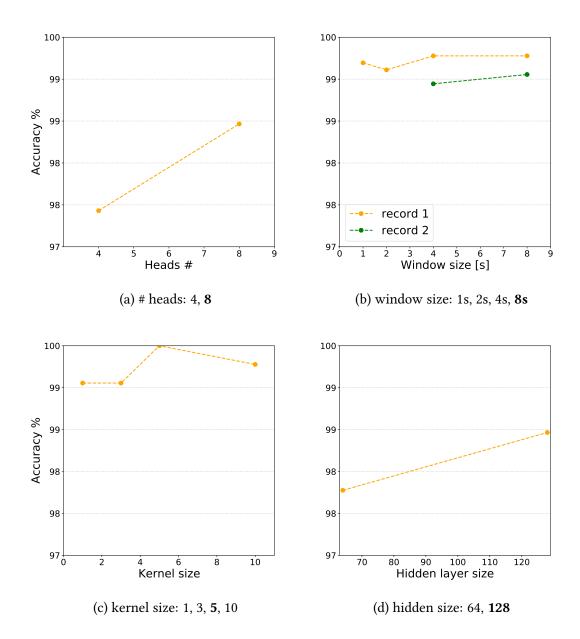

|   |     | 5.2.1    | EEGformer                                      | 86 |

|   |     | 5.2.2    | CNN on raw EEG signal                          | 89 |

|   |     | 5.2.3    | CNN on pre-processed input features.           | 89 |

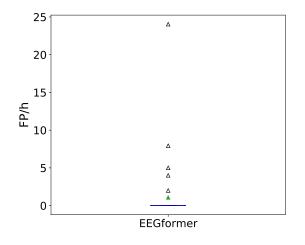

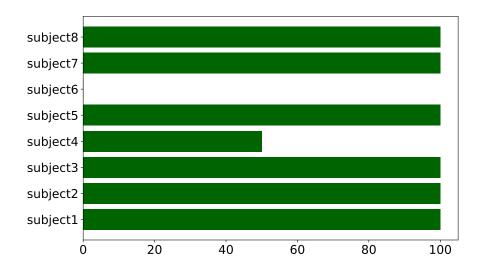

| 5.3 | Assessment on CHB-MIT dataset |                                        |    |  |  |

|-----|-------------------------------|----------------------------------------|----|--|--|

| 5.4 | Deploy                        | yment                                  | 94 |  |  |

|     | 5.4.1                         | Deployment on Apollo4                  | 94 |  |  |

|     | 5.4.2                         | Deployment on GAP: exploit parallelism | 94 |  |  |

|     | 5.4.3                         | Closing remarks                        | 95 |  |  |

|     |                               |                                        |    |  |  |

## 6 Conclusions

### Abstract

The design of a Convolutional Neural Network suitable for efficient execution on embedded edge-processing platforms requires reconciling accuracy and efficiency requirements. Several research efforts have translated this task into the iterative search of Pareto-optimal points satisfying multiple objectives, but a step forward is still needed to assist the developer in this complex task. In this thesis, we summarize the key challenges of edge-oriented design into three main topics.

As a first point, the size of the design space is so big it makes any full exploration unfeasible, thus, effective practices to limit the exploration time without compromising its outcome are needed.

Additionally, edge-processing platforms are highly heterogeneous and often endowed with specialized accelerators, therefore the prediction of the hardware performance of the candidate design points requires a certain degree of platform awareness.

Finally, the recent advancements in the neural network domain have uncovered emerging models and intelligence mechanisms, whose success has encouraged their optimization for deployment at the edge. The transformer represents a remarkable example.

In this thesis, we present our contribution to these relevant design challenges. First, we describe an efficient design flow to jointly evaluate several design parameters, referring to a Keyword Spotting task targeting a commercial micro-controller for its evaluation. We provide a fast exploration strategy, requiring around 30 hours and resulting in state-of-the-art accuracy within the defined storage constraints. We further consider a more accurate exploration strategy, allowing us to refine the performance evaluation during the search process with an additional characterization time.

As a second contribution, we present an accurate, flexible, and easy-to-use estimation method for the most relevant hardware performance metrics, such as latency, energy consumption, and throughput, to be integrated into an automated design flow and enable modeling the network execution on the most typical families of edge-processing devices. The proposed method improves the prediction accuracy of state-of-the-art approaches of comparable complexity, not requiring access to direct on-hardware measurements during the exploration process, and improves by up to  $4 \times$  the predictability of hardware-aware Neural Architecture Search.

As the last contribution, we present a tiny transformer model for long-term epilepsy monitoring, suitable for real-time seizure detection on low-power health-monitoring devices. The assessment of its performance shows accuracy metrics well-aligned with the state of the art, obtainable with as low as 13.7ms inference time and 0.19mJ energy consumption per inference.

# Chapter 1

# Introduction

Convolutional Neural Networks (CNNs) have represented for years the state of the art in the image classification [1, 2, 3, 4] and object detection [5] tasks, thus becoming one of the standard approaches to computer vision in various fields, from autonomous driving [6] to medical imaging [7, 8]. Their success is not strictly limited to image processing, as they have been also successfully applied, among other fields, to speech recognition [9, 10] and medical signals processing [11, 12].

The ability to learn complex data representation is obtained through complex architectures stacking multiple computational intensive operators, dominated by convolutions, which require the storage of a significant amount of trainable parameters. To give an example, the ResNet-50 architecture employs 26 MB of parameters and requires 4.1 billion of Floating-Point operations (FLOPs) [13].

Despite such high computational and storage requirements, the growing success of CNNs has encouraged their deployment on a variety of different processing systems, including the edge-processing domain. This deployment scenario introduces tight resource constraints, requiring careful optimization of the classifier design and representing a very challenging task. As the range of CNN-based applications grows, there is a need for efficient design solutions to assist the system developer in defining the optimal CNN architecture to meet the accuracy and performance constraints.

Despite the ongoing research efforts, edge-oriented design still presents two key challenges. The first one is represented by the huge design space of architectural and processing possibilities: the CNN structure is obtained as the composition of multiple stages, each applying different transformations to the input data; the different combinations of parameters (shape and operand) for each stage, as well as their number and sequence, result in a wide range of different models, reaching different levels of accuracy and representing a different computational workload. Moreover, the system design should also consider any data preparation stage, as well as any possible optimization step which could be applied to a candidate CNN model, to reduce its computational or storage requirement.

At the same time, the constrained deployment scenario demands a tight trade-off between the complexity and the accuracy of the classifier. However, the edge-processing domain is a composed set of hardware targets, exploiting computing units based on different architectural solutions, thus the comparison of the efficiency of two alternative CNN models is a non-trivial task, where the specific characteristics of the target hardware have to be taken into account. These main points can be summarized as the need to provide an efficient design exploration strategy, and the need to enable a certain degree of platform-awareness.

Furthermore, the continuous advancements in the neural network subject have introduced new operands and architectural solutions, which enrich the CNN baseline of new features and capabilities. The transformer represents a relevant example, as it has recently challenged the supremacy of CNNs in some of the most relevant application fields. The interest in this emerging model has grown to include edge deployment, thus the optimization of its architecture for the target domain has become a relevant subject.

In this thesis, we mean to contribute on these challenges. Our contributions can be outlined in three points:

- the definition of an effective design exploration strategy, comprehensively considering the effects of tuning the available design parameters on the performance and efficiency of edge implementation, within a limited exploration time [14];

- the development of an accurate estimation method to predict the on-hardware efficiency of a candidate design point on a given target platform[15];

- the application of hardware-aware design to a transformer architecture [16]; the optimization process resulting in the proposed architecture does not exploit the design

flow presented in [14], but it shows that very similar concepts apply to this family of networks.

Here we briefly describe the organization of the following pages. In Chapter 2 we revise the state of the art of edge-processing platforms and neural networks optimization strategies, focusing on automated design based on Neural Architecture Search (NAS) and considering platform awareness. In Chapter 3 we present our design procedure, describing two different implementations representing different trade-offs between exploration effort and the quality of the resulting design. We refer to the ALOHA framework (Software framework for runtime-Adaptive and secure deep Learning On Heterogeneous Architectures<sup>1</sup>), which provided the context and reference for the contribution presented in this chapter. In Chapter 4 we describe our ALOHA estimation method for the prediction of platform-aware metrics, aiming to enable hardware awareness in NAS-based design targeting the embedded domain. In Chapter 5 we present an optimized transformer model designed for epilepsy monitoring on low-power devices. Finally, the conclusions are summarized in Chapter 6.

<sup>&</sup>lt;sup>1</sup>https://www.aloha-h2020.eu/

# **Chapter 2**

# State of the Art

In recent years there has been a growing interest in enabling artificial intelligence on tiny smart devices, providing near-sensor processing and thus reducing the power consumption of battery-powered devices, easing the bandwidth requirements of a cloud-based processing system, and ensuring the privacy and security of the user's sensitive data [17]. All these aspects are of particular relevance in some application fields, including industrial applications [18] and health-monitoring [19].

In the following, we start with a brief review of the state of the art of efficient edgeprocessing platforms specialized for the neural networks' workload, in Section 2.1. Then, we focus in Section 2.2 on the network model optimization, considering network compression (Section 2.2.1) and automated design based on Neural Architecture Search (Section 2.2.2). In Section 2.2.3 we revise the literature of the existing approaches enabling platform awareness in the NAS process, whereas we summarize in Section 2.2.4 the most relevant works exploiting NAS for the design of an efficient Keyword Spotting (KWS) classifier, as we will reference a KWS use case for the definition and evaluation of our design strategy. Finally, we discuss in Section 2.3 some relevant works dealing with the transformer model and its current application scenarios.

## 2.1 Edge-processing Platforms

The recent trend to enable artificial intelligence capabilities on low-power tiny devices, fitting the size and energy requirements of the edge-computing paradigm, has encouraged the design of an abundance of specialized computing platforms for the efficient execution of neural networks (NNs). The work of [20] provides a very recent survey on the most popular hardware platforms for edge NN-inference. This rich landscape includes several solutions, representing an effort toward adjusting the computational power of the target devices to the typical workload of neural networks, dominated by convolutions and matrix multiplications [21]. In the following, we list some of the solutions available, such as:

- application-specific accelerators, like Google Edge TPU [22] and NVIDIA Deep Learning Accelerator (NVIDLA) [23], optimized to reach high performance in the execution of tensor processing operations;

- systems-on-chip, such as Intel Movidius [24], a highly optimized video processing unit based on 16 cores and a dedicated hardware engine for neural networks acceleration, and Qualcomm's Snapdragon [25], targeting gaming applications and embedding a specialized accelerator;

- tiny GPUs, such as NVIDIA Jetson [26];

- several development boards based on micro-controller units (MCUs), such as ST Sensortile [27] and Ambiq Apollo4 [28], as well as on parallel computing clusters, like Greenwaves GAP processors [29], supporting Single Instruction Multiple Data;

Along with commercial devices, several academic research prototypes have been proposed, such as the Eyeriss flexible application-specific accelerator [30], or FPGA-based computing engines, like the one presented in [31] and NEURAGHE [32]. The computing platforms can support different data precision: for example, NVIDLA natively supports various data types, including 2-, 4-, 8-, 16-bit integer representations, and 16-, 32- and 64-bit floating point representation [23].

In most cases, high performance is obtained thanks to parallel computing on dedicated accelerators. In order to exploit at best the performance enabled by these specialized comput-

ing units, efficient dataflows optimizing the use of the hierarchical memory systems and the communication resources need to be implemented [30]. Due to this reason, the wide range of hardware solutions is accompanied by a family of specialized software libraries enabling efficient access to the computing resources: representative examples are cuDNN [33], targeting GPUs, CMSIS-NN [34], specifically optimized for the ARM Cortex-M family of cores (like the one embedded in the SensorTile), and the PULP-NN library [35], targeting PULP-based clusters (like the GAP processors).

## 2.2 CNN model optimization

Alongside the design of more efficient computing architectures, a parallel line of research deals with the optimization of deep network structures into more portable models, which remains a primary concern to fit the low-power requirements of several application scenarios, as well as the size of local storage resources close to the computing engines. The constraints on the memory footprint are especially hard when tiny MCUs are targeted, motivating the studies related to more lightweight, yet accurate and efficient, network architectures. Popular examples of handcrafted tiny network models targeting classification and object-detection on the edge-domain are SqueezeNet [36], reaching the 80.3% top-1 accuracy on the ImageNet dataset [37] for image classification with  $50 \times$  fewer parameters than the comparable AlexNet [1], the MobileNet family [38], reaching up to 75% accuracy with 5.4M parameters, and TinyYolo [39], requiring 8.9 MB and reaching 34% mAP on the COCO dataset [40].

### 2.2.1 Network compression

Along with the time-consuming design-from-scratch approach, compression techniques reducing the size of common network models have captured great interest. The rationale of network compression is that neural networks are highly redundant: quantization exploits the robustness deriving from such redundancy to reduce the precision of the parameters representation, and consequently the memory requirements of the network model. The groundbreaking work of [41] showed how the combination of connections pruning and data quantization could be exploited to reduce by  $35 \times$  the storage requirements of AlexNet [1] without affecting its accuracy on the ImageNet dataset [37].

A very recent survey on the current approaches to quantization is provided in [42]. The main concept is to map the real values to a reduced precision interval, based on a scaling factor and a zero point. A relevant work for the selection of the representation interval is represented by PACT [43], addressing the challenge of quantizing the activations through an optimal scaling factor learned during training. The authors show that full-precision accuracy can be obtained with as low as 4-bit representation, considering the performance of AlexNet, ResNet-18, and ResNet-50 on the ImageNet dataset [37]. This line of research is called Quantization-Aware Training, allowing the recovery of the accuracy loss resulting from the reduced precision with an additional computational cost. Despite the relevant results obtained in [43], with commonly available methods lossless quantization can be easily achieved up to 8-bit representation, whereas recovering the accuracy drop resulting from more aggressive strategies is still not straightforward.

### 2.2.2 Hardware-Aware Neural Architecture Search

Even with the support of these common compression methods, the design of a network architecture targeting a given application on a specific hardware platform is a complex task, requiring much application- and NN-related expertise. The work of [44] introduced NAS as an automated design procedure, defined as an iterative search process and based on the definition of a *search space*, a *search strategy*, and a *performance evaluation* model. Exploiting a Recurrent Neural Network (RNN) as a controller, to first generate CNN models as design points in the search space and then evaluate them based on their expected accuracy, the authors improved the state-of-the-art CNN on the CIFAR-10 dataset [45], selecting the best network architecture among 12800 model configurations. Moving from this first single-objective approach [46, 47], hardware-aware NAS (HW-NAS) [48] includes the on-hardware performance metrics in the search loop, considering the Pareto-optimal points in terms of validation accuracy and an additional hardware-related cost function. In the following, we discuss some of the most relevant works on HW-NAS.

The authors of [49] studied a compound scaling method, to obtain new versions of known CNN architectures based on the hardware requirements by jointly scaling the depth, width, and resolution of the baseline network. When applied to state-of-the-art networks, like MobileNet and ResNet, compound upper scaling allows obtaining up to 5% accuracy improvement. After applying NAS optimizing accuracy and OPS, they select a family of networks, the EfficientNets, which reduce by around an order of magnitude the number of OPS of stateof-the-art models with comparable accuracy. As OPS count does not allow for an accurate performance estimation on the target hardware [50], other approaches consider direct onhardware measurements during the exploration process: the authors of [51] consider direct hardware measurements of latency on target mobile devices, resulting in the design of MNas-Net, reaching 75.2% ImageNet accuracy with  $1.8 \times$  speedup over MobileNetV2 [52]; in [53] peak power and average energy consumption measurements are included in the reward function to evaluate the candidate networks during the exploration.

The literature reports many other examples of works relying on HW-NAS for optimal network design, considering different performance metrics estimations [54, 55, 56, 57, 58, 59]. The subject of hardware performance modeling will be further discussed in Section 2.2.3.

As an application-specific NAS could require a huge amount of iterations, several solutions have been proposed for the search optimization, exploiting one-shot training and weight sharing [59, 60]. The OFA framework [59] allows defining the design space as a super-network, which is trained once to optimize all its possible sub-networks, representing the candidate design points. Considering several deployment scenarios, the authors exploit a single training procedure to select the optimal network targeting CPUs, GPUs, and FPGA accelerators, based on an accuracy predictor and on latency look-up-tables (LUTs). They obtained up to 4% ImageNet accuracy improvement over MobileNetV3. Finally, to keep up with the wide adoption of reduced-precision CNNs, some automatic design flows also consider compression through quantization, as an optimization objective along with network topology selection [61, 62].

In this thesis, considering the lesson of [59], we present an efficient design space exploration to address the selection of multiple design knobs in a target-oriented CNN optimization problem. As we selected a KWS task as a target use case, we will further discuss the comparison with NAS oriented to the KWS problem in Section 2.2.4.

| Category            | Methods                                     | Metric                     | Accuracy               | Re-usability | Modularity |

|---------------------|---------------------------------------------|----------------------------|------------------------|--------------|------------|

|                     | [49]                                        | latency                    |                        |              |            |

| OPS                 | [63]                                        | latency, energy,<br>memory | low                    | very high    | X          |

| Roofline            | [64]                                        | latency                    | medium/ low            | high         | ×          |

| Specialized         | Specialized [65] latency, energy,<br>memory | medium/                    | low                    |              |            |

| analytical          | [56, 66]                                    | latency,energy             | high                   |              | X          |

| methods             | [54, 55, 67]                                | latency, energy            |                        | medium       |            |

|                     |                                             | throughput                 |                        |              |            |

| Measurements        | [57]                                        | latency                    | high                   | very low     | ×          |

| <i>Meusuremenus</i> | [53]                                        | latency, energy            |                        | very low     |            |

| Look-up tables      | [59]                                        | latency                    | high                   | low          | ×          |

| (LUT)               | [68]                                        | latency                    | high                   | medium/ low  | X          |

| M                   | [69]                                        | latency, energy            | high                   | very low     | v          |

| ML                  | [70]                                        | latency                    |                        |              | X          |

|                     | this thesis                                 | latency, energy            | / medium/<br>high high |              |            |

| ALOHA               | <b>Ch.</b> 4                                | throughput                 |                        | nıgn         | <b>v</b>   |

Table 2.1: Comparison of methods for evaluation of platform-aware CNN metrics

### 2.2.3 Hardware cost modeling

Platform awareness represents a key point in most of the recent works dealing with an optimal design based on NAS. Table 2.1 provides an overview and comparison of the methods commonly exploited in the literature for the evaluation of platform-dependent CNN metrics. The state-of-the-art estimation methods, listed in Column 2, are grouped into general hardware-performance modeling categories, indicated in Column 1. The examined works are associated with the list of platform-aware metrics they are able to capture, given in Column 3, and compared in terms of their accuracy (Column 4), degree of re-usability (Column 5), and level of modularity (Column 6).

A high re-usability is an important quality metric, limiting design-time overheads despite the ever-increasing number and diversity of CNNs and target hardware platforms, and refers to how many different ones can be successfully modeled with the considered method. To give an example, the operations count (OPS) category (Row 2) has very high degree of re-usability because it is easily adaptable to a variety of CNNs and hardware platforms without requiring any changes. On the other hand, the methods based on machine learning (ML) predictors (Rows 12 to 13) exhibit very low re-usability because, once designed, the predictors are only applicable to a specific set of explored CNNs and a specific target platform, and if that set is changed they must be completely redesigned.

The modularity item, in Column 6, refers to the modeling power of the method, considering whether it can account for the modular structure of the platform, including the distribution of the layers over the different processing units in a heterogeneous platform, and their execution schedule. Based on the typical scheme adopted in common Deep Learning (DL) frameworks, such as Pytorch [71] or TensorFlow [72], CNN inference is usually sequential. Thus the platform accelerators receive the workload layer-by-layer [73]. However, as suggested in [17], efficient edge-processing can be achieved with different scheduling choices [74, 75, 76], improving the throughput and energy consumption, and thus requiring consideration when the hardware-aware metrics are estimated.

In the following, we will briefly comment on and compare the considered modeling categories, referring, for brevity, to latency estimation. As already mentioned, estimating inference latency based on the network OPS is a simple and highly reusable method. However, the obtained predictions are often inaccurate [50, 51], introducing a significant error margin between the predicted latency and the one measured on the target platform. When the design targets applications with severe timing and resource constraints, as is common in autonomous driving [77] or object recognition on drones [78], this would result in the need to replace the selected CNN model.

We indicate as Roofline methods (Row 4) those evaluating latency based on the well-known Roofline model [79]. These methods consider the impact of memory access in addition to the number of OPS required by the network, providing a more precise latency evaluation. However, the estimation accuracy is still not sufficient to correctly model the hardware performance of some CNN models on particular hardware platforms.

Rows 5 to 7 refer to specialized analytical methods producing latency estimations based on exact hardware platform representations. The increased estimation accuracy is obtained at the expense of a low re-usability. To give some examples, in [54, 55, 56] a precise roofline-based model is exploited for FPGA co-design, whereas [67] relies on the MAESTRO model [80] for ASIC co-design. If different hardware platforms are targeted, such as CPUs or GPUs, these models can't be exploited or would require adequate adaptation.

In Rows 8 and 9 we list studies including direct on-hardware latency measurements in the design process. Based on a similar approach, works in Rows 10-11 access LUTs collecting measured latency values for single layers, or blocks, to evaluate the overall network latency. This solution ensures the best accuracy, however, it requires a large number of measurements [57, 53], or a narrow exploration based on a small LUT.

Finally, ML predictors (Rows 12 to 13), such as neural networks or regression models, can be very accurate, but they need to be trained on a large number of measurements and provide very low re-usability. Some examples of required profiling time are reported in Table 2.2. We assume an average inference time of 15ms and evaluate the data collection time of the considered works, which would be over 1 hour for [81], and over 18 hours in [57]. This is a very soft hypothesis, as [70] reports almost 2 weeks of data collection time. In general, training has to be repeated for each target platform, although some approaches suggest a training procedure considering a range of targets (e.g. [69] evaluates 447 different GPU configurations, while [81] suggests training a single network for predicting performance on multiple hardware).

In Chapter 4 of this thesis, we propose a platform-aware evaluation model to be efficiently included in the HW-NAS loop, able to provide realistic predictions of the critical performance metrics, like latency, energy consumption, and throughput. Being based on abstract high-level platform specifications, it can be applied to a wide range of hardware platforms, without requiring repeated measurements.

| Method | Data Collection time      | Training time      |  |

|--------|---------------------------|--------------------|--|

|        | $n\_sample * t * N_{avg}$ |                    |  |

| [81]   | 75000 * t * 5             | (300 epochs)       |  |

| [70]   | $80000 * t * N_{avg}$     | 1h (1000 epochs)   |  |

| [57]   | 90000 * t * 50            | 20min (150 epochs) |  |

| [69]   | $447 * 108 * t * N_{avg}$ | not specified      |  |

Table 2.2: The required profiling time for the evaluation methods based on ML models is described as the sum of two major components: the time required to acquire the training data, and the time required to perform the training procedure. The Data Collection time is expressed as the product of 1) the number of samples evaluated,  $n\_sample$ , 2) their execution time on the target hardware, t, and 3) the number of times each measure is repeated to obtain an accurate value,  $N_{avg}$ .

|        |           | Quantization |             | Pre-processing |                |             |

|--------|-----------|--------------|-------------|----------------|----------------|-------------|

|        | Hardware  | Levels       | Cross       | Parameters     | Cross          | Exploration |

|        | metric    |              | exploration |                | exploration    | description |

| [61]   | OPS       | 8bit         | ×           | n. frames      | 1              | ×           |

|        | footprint |              |             |                |                |             |

| [62]   | OPS       | up to 1bit   | ×           | not applicable | not applicable | 1           |

|        | latency   |              |             |                |                |             |

| [82]   | OPS       | X            | ×           | ×              | ×              | 1           |

| [83]   | ×         | X            | ×           | ×              | ×              | 1           |

| this   | latency   |              |             | feature type   |                |             |

| thesis | footprint | up to 4bit   | 1           | n.features     | 1              | 1           |

| Ch. 3  | energy    |              |             | n. frames      |                |             |

### 2.2.4 Neural Architecture Search for KWS

Table 2.3: Comparison with state-of-the-art works on NAS targeting KWS.

KWS utilities are typical examples of applications to be deployed on power-constrained edge devices, often having limited storage resources. Thus the design of new workload-efficient network architectures, either handcrafted [84] or resulting from NAS [61, 82, 83, 62], was encouraged. We will discuss in the following some relevant examples of the latter, which

provide a comparison reference for the design strategy presented in Chapter 3 to efficiently address the hardware-oriented design of a KWS system.

The state of the art is summarized in Table 2.3: the main works, listed in Column 1, are compared in Column 2 based on the metrics captured by their degree of platform awareness. Columns 3 and 4 refer to the quantization subject: we indicate the range of representation precision explored and whether the exploration of the CNN topology and the quantization policy is combined. Columns 5 and 6 report similar information about the pre-processing scheme, considering the most common speech features, namely Mel energies and Mel-Frequency Cepstral Coefficients (MFCC). Finally, Column 7 highlights the works providing methodological guidelines for the exploration. We briefly comment on the referenced studies in the following.

The work of [61] compares different network models obtained through NAS, considering CNNs, depth-wise separable CNNs (DS-CNNs), RNNs, and deep neural networks (DNNs). The exploration targets MCUs embedding ARM Cortex-M Processors of different sizes, defined as Small, Medium, and Large, integrating hardware awareness as a set of constraints on the number of OPS and the memory footprint. The pre-processing scheme assumes feature extraction based on MFCC, where the number of frames constituting the spectrogram is subject to exploration, resulting in a 49x10 (49 time-frames and 10 features) resolution for every evaluated model. Quantization is performed only on the finally selected model, up to 8-bit representation. The focus of the work is not on providing design guidelines, as it aims to present the well-known state-of-the-art DS-CNN architectures, reaching higher accuracy than the corresponding CNN candidates.

The authors of [62] exploit differentiable NAS based on OPS evaluation to design a CNN model reaching 95.6% accuracy, with 75.7KB of parameters and 13.6 MOPS. It is applied to raw audio files, leveraging learned parameterized *SincConv* functions executed as a first stage. Thus, this pre-processing approach can not be described according to the scheme proposed in Columns 5 and 6 in Table 2.3. Also in this case, quantization is only applied to the selected CNN model, thus it is not cross-explored with the topology: the best performing quantized version exploits 2.51-bit weights and 2.91-bit activations, reaching 93.76% accuracy.

OPS is again the reference hardware evaluation metric in [82]. This work describes an exploration methodology based on two stages: a first fixed-budget training phase, and a second refinement step on the Pareto-optimal candidates, based on hyperparameters subject to exploration. The provided guidelines do not address the cross-exploration of the pre-processing scheme or the quantization policy, considering pre-processing based on MFCC and resulting in 40x32 feature resolution. The best-performing CNN reaches 95.1% accuracy.

As a last reference, we consider [83], presenting a model based on depth-wise separable and dilated convolutions which reaches 97.2%. Until recently, this was the state-of-the-art for convolution-based KWS models. It requires pre-processing based on MFCC, resulting in 101x40 input features. Such pre-processing scheme is pre-defined when the NAS exploration is performed.

To the best of our knowledge, as summarized in Table 2.3, ours is the first approach to provide methodological guidelines on how to efficiently combine the exploration of the optimal CNN topology, pre-processing scheme, and quantization level, considering hardware-aware performance evaluations. We believe that the impact of feature extraction and input resolution on the final accuracy and overall performance motivates our perspective, as both the inference time and storage resources are affected by these design choices. To refine the OPS indirect complexity metric into a more accurate execution time estimation, easily comparable with a maximum constraint, we exploit a latency prediction model of the target platform. Furthermore, the current trend [85] shows the importance of including quantization within the NAS exploration. We mean to extend such benefits to the KWS field.

## 2.3 Emerging Neural Networks

In the last years, the landscape of neural networks has evolved far beyond the simple CNNs, to include more complex and irregular models enforcing new intelligence mechanisms.

Nowadays, the transformer has gained momentum since its first appearance in the work of [86]. The attention mechanism, representing the core of the transformer, was first applied to machine translation tasks, providing state-of-the-art results thanks to a general understanding of the context.

Recent works have applied the same mechanism to other fields. The most renowned example is represented by the Vision Transformer [87], proposing a transformer architecture applied to the image classification problem. Ever since, less conventional application fields have been studied, such as audio processing [88], and medical signal processing [89, 90, 91, 92]. This spread to include new use cases has contributed in pushing toward edge deployment also for transformer-based models [93, 89], requiring specific quantization strategies [94].

In Chapter 5 of this thesis, we finally consider the optimization of a transformer model targeting the epilepsy monitoring problem on the wearable domain, based on the typical storage constraints of tiny MCUs. The presented use-case allows to highlight the design knobs available for hardware-oriented optimization and the similarities with the CNN domain. Although the presented exploration was not conducted with the tools introduced in Chapter 3, the advantages of such a design approach could be exploited also for transformers, once the support for the specific operands is integrated.

# Chapter 3

# Optimizing the design space exploration: the ALOHA design flow

One of the main challenges of edge-oriented design is the huge amount of design parameters deeply affecting the performance of the system, whose exploration would be enormously time-consuming, thus requiring efficient exploration strategies. A well-suited example for the discussion of platform-aware design and optimization of efficient CNN-based system implementation is represented by the KWS task. It consists of a simple speech recognition problem, requiring the classification of a limited set of instructions[95], or the detection of few wake words, as in smart home devices, where it is coupled with more complex audio processing systems running on the cloud. We consider this use case as a reference for two main reasons:

- the various applications relying on KWS provide multiple deployment scenarios, targeting a very wide range of processing platforms and hardware architectures, which should be precisely characterized to enable efficiency evaluations within the design flow;

- 2. KWS classification based on CNNs usually exploits feature-extracting techniques, representing additional design choices to be considered.

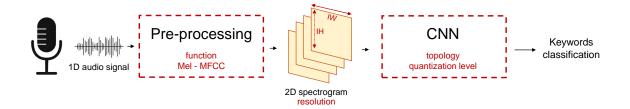

The general composition of a KWS system is highlighted in Figure 3.1: the recorded audio samples are streamed to a pre-processing stage, responsible for extracting representative features, which are provided to a CNN-based classification stage and thus assigned to a set of classes corresponding to the keywords to be recognized. Restricting the classifier space to

Figure 3.1: KWS system overview.

the CNN domain, an effective system design exploration should involve several parameters, impacting its performance on the target hardware:

- the feature-extracting function we assume as reference the most common preprocessing functionality in literature, which converts the audio stream into a bidimensional representation of the power spectrum of the acquired audio over time, namely Mel energies and Mel-Frequency Cepstral Coefficients (MFCC);

- the resolution of the extracted features;

- the CNN topology;

- the CNN quantization level.

The vast design space resulting from all their possible combinations cannot, in general, be fully explored. In this thesis, we present a design flow to efficiently address the design of platform-specific applications, considering the KWS reference use case and targeting deployment on a tiny Micro-Controller Unit (MCU). Our proposed strategy allows to reach near-optimal solutions based on the evaluation of a restricted number of network candidates. The backbone of optimization tools is provided by the ALOHA framework, which is the result of a research project with several contributing partners, aiming to facilitate the design and deployment of efficient, yet accurate, CNN models on a desired target embedded platform [96]. Based on a combined effort with the research team of Santer Reply SpA, we defined an efficient design flow combining the tools in ALOHA, able to:

- consider target-awareness: predicting the effects of the different design choices on targetdependent metrics such as latency, footprint, or energy consumption, based on a modelbased evaluation tool whose estimations are included in the optimization process;

- enable the combined *cross-exploration of the data pre-processing, the CNN topology, and the quantization*, as the combination of these design choices impacts the classification accuracy and the hardware efficiency.

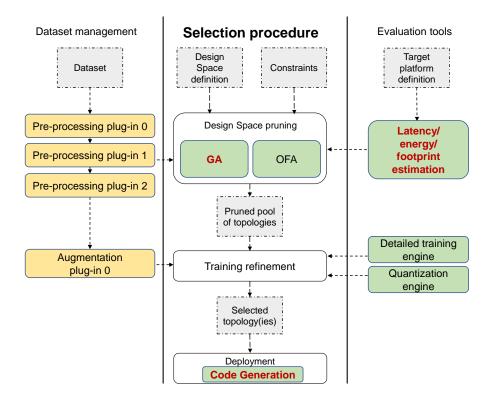

Rather than in the introduction of one specific tool, the contribution analyzed in this chapter lies in the definition of an effective strategy, based on an HW-NAS approach, to exploit the feedback provided by the set of available evaluation tools and define a restricted set of network architectures to which the most time-consuming refinement steps should be applied. Nonetheless, some of the tools were specifically extended to provide the results disclosed in this chapter, as is detailed in the description of Figure 3.2.

Based on the design effort, we define two different versions of the design flow. The first one implements a *fast selection* procedure, detecting at-least-sub-optimal solutions with a limited exploration time. The second one involves a more precise characterization phase considering the accuracy drop connected to quantization: we refer to it as *accurate selection*.

In the following, after a brief description of the reference platform, we start with a general overview of the ALOHA framework, provided in Section 3.1, introducing the tools available for network optimization and performance evaluation. The proposed design strategy, configured as the fast and accurate implementations of our hardware-aware CNN selection procedure, is described in Section 3.2. Finally, experimental results are presented in Section 3.3. As most of the state-of-the-art works, the classification task refers to the Google Speech Commands dataset [95], and involves 10 of the 35 classes provided: "Yes", "No", "Up", "Down", "Left", "Right", "On", "Off", "Stop" and "Go", plus the additional classes "silence" and "unknown".

### SensorTile

As an example target of our design-flow application, we consider a tiny microcontroller platform, developed by STMicroelectronics: the SensorTile. It is an IoT module, equipped with a digital microphone, and embedding an 80 MHz ARM Cortex-M4 32-bit low-power micro-

Figure 3.2: Selection procedure for target-oriented CNN design exploiting the ALOHA framework. The main stages of the evaluation procedure are depicted as white boxes, whereas the required inputs to the various stages of the exploration are represented as grey boxes. Yellow boxes represent the dataset management utilities, whereas green boxes represent the tools available on the framework for the evaluation of the candidate network models. We highlighted in red the tools specifically extended to enable the exploration described in the following sections.

controller, accessing a 96kB SRAM, and 1MB FLASH memories, posing strict storage constraints. The system architecture exploits a Real-Time lightweight Operating System (RTOS), providing support for multi-threading, and scheduling of the different application tasks on defined timings. For efficient CNN execution, we relied on the CMSIS-NN library [34], specifically developed to target this family of processors.

## 3.1 ALOHA CNN design flow

The ALOHA framework exploits NAS to address CNN design as an iterative selection process. Figure 3.2 depicts an overview of the framework organization. The optimization process starts from the following list of inputs:

- a reference dataset a collection of data to be manipulated with the desired set of preprocessing operations;

- a platform description defining the hardware resources, exploited to obtain reliable hardware-related performance metrics;

- a set of constraints defined based on the platform's description and the application requirements and translated into a maximum inference latency and memory footprint;

- a design space definition a set of CNN topologies and operands to be explored.

The design flow is configured as a *Selection Procedure* which considers the set of design constraints and the definition of the reference design space to search for the optimal CNN candidate, identified based on several iterations of refinement sub-steps. It is served by a *Dataset management* utility, selecting for the different training actions the pre-processing and datalevel transformations to the reference dataset, which defines the CNN-application task. Moreover, the *Selection Procedure* relies on a set of *Evaluation tools* to accurately compare the design points with each other based on the estimation of the most relevant metrics.

In the following, we outline in more detail the features of the tool flow components.

### 3.1.1 Dataset Management Utility

The ALOHA tool flow enables the customization of the data pre-processing operations according to the application's requirements [97], as showed in the *Dataset management* column of Figure 3.2. In detail, it describes as a plug-in each transformation or pre-processing operator which can be applied to the data, based on the user definition. The plug-ins can be treated independently and arbitrarily connected to others into a *pre-processing pipeline*, which can be applied at sample level, or batch level. For the KWS use case, the *pre-processing plug-ins*  include the feature-extraction functions applied to the audio samples, combined with several *augmentation plug-ins*, like random time shifts, random noise addition, random pitch, and random speed.

### 3.1.2 Selection Procedure

The *selection procedure* is described in the central column of Figure 3.2. It requires the definition of a reference *Design Space*, and possible design *Constraints*, resulting from the performance requirements of the application, or the resources available on the target hardware.

The constraints definition induces a *Design space pruning* to identify a reduced pool of eligible near-optimal CNN topologies. This step exploits a *Genetic Algorithm* (GA) to surf the search space, ranking and refining the candidate populations of CNNs. As the exploration includes a big number of design points to be compared, their accuracy is assessed at this stage using an efficient one-shot training utility, the *Once-for-All* (OFA) [59], whereas the hardware metrics are estimated based on a target-aware *Latency/ energy/ footprint evaluation* tool.

Finally, a refinement phase is performed on the pruned pool of design points, to precisely assess their accuracy with a *detailed training* and a *quantization* step, reducing their memory footprint: one or more CNN architectures can be selected for *Deployment*.

### The OFA training

The one-shot training enables efficient NAS over large design spaces. As anticipated in Section 2.2.3, OFA [59] allows describing the search space as a single SuperNetwork and the design points as all its possible subnetworks. All the models in the design space are thus trained with a single training procedure, requiring a reasonable amount of time, as we will further discuss in Section 3.3.1. The subnetworks are optimized through weight sharing, starting from those having the highest number of parameters, and finally adjusting the accuracy of the smallest ones. This is achieved by considering elastic parameters, such as the kernel size, network's depth, and width. The accuracy of each design point can be assessed by just performing inference over the validation set, which is significantly less time-consuming than repeating an independent training for each design point.

### The genetic algorithm

The GA provides a search strategy, selecting populations of design points satisfying the search criteria and updating them. Admittance into the eligible population is evaluated based on accuracy, latency, memory, and energy estimations. The new generations are obtained as the composition of the most accurate points evaluated up to that point, and of new network models randomly obtained with mutations on the parameters of those most promising points. In this work, we consider flexible and independent mutations involving the pre-processing pipeline, the input resolution, the kernel size, the number of convolutional layers, and their width. Thus, the search is guided to the selection of the most suitable candidate points, having the highest validation accuracy within the defined constraints.

### 3.1.3 Evaluation tools

The right column of Figure 3.2 lists the *Evaluation tools* available for the pruning and refinement phases.

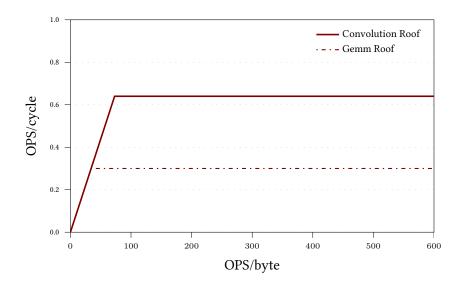

#### The Latency estimation tool

The *Latency estimation tool* enables hardware-aware performance estimation based on the CNN's parameters and the target platform description. For the NAS targeting SensorTile presented in this Chapter, inference time is evaluated exploiting a simple Roofline-based [79] model, shown in Figure 3.3. The main concepts of the Roofline model are recalled in Section 4.1.3. For the SensorTile, we assessed two distinct performance roofs, representing the maximum achievable performance for convolutional and fully connected operands, set respectively to 0.64 ops/cycle, and 0.3 ops/cycle. This model enables latency estimations having an average 25% error, evaluated on a set of 450 common convolutional layers, and 60 fully connected layers, in comparison to direct measurements.

The tool considers the impact of the different quantization levels on the memory footprint, evaluated assuming a double buffer mechanism for the activations. While the metrics considered in this Chapter do not include energy consumption, a more detailed discussion on the topic of platform-aware performance modeling will be explored in Chapter 4.

Figure 3.3: Roofline model of the SensorTile platform, representing peak performance roofs for Convolution and Gemm execution.

### The Detailed training engine

The *Detailed training engine* allows reaching higher accuracy values than the one-shot training, thanks to the possibility to exploit data augmentation techniques, as supported by the Dataset management plug-ins, although requiring a longer time. It is thus exploited in the refinement phase and applied to a limited set of candidate points. It accepts network models in the ONNX (Open Neural Network Exchange) format [98], and can be exploited to further improve the accuracy of pre-trained models [99].

### The quantization engine

The *Quantization engine* is based on the NEMO (NEural Minimization for pytOrch) framework [100], relying on PACT (Parameterized Clipping Activations) quantization [43], whose main concepts were anticipated in Section 2.2.1. To allow quantized representation for the activations and not only the weights, in the resulting network model some operators, such as Batch Normalization (BN) and ReLU, are replaced respectively with a sequence of Mul/Add and Mul/Div/Clip operators.

### 3.1.4 Deployment

Finally, ALOHA provides a target-oriented *Code generation* tool, to automatically obtain efficient and fast deployment. The tool consists of a Python script generating, from a network model in ONNX format, an intermediate generic representation of NN operators and preprocessing functions, which is finally translated into a C implementation exploiting the specific target-compliant functions, providing the source code for the inference execution as well as the appropriate arrangement of the parameters. In this chapter, we exploited generation targeting SensorTile, based on the CMSIS-NN library [34], slightly modified to efficiently handle the quantized models produced by the quantization tool.

## 3.2 CNN selection procedure implementation

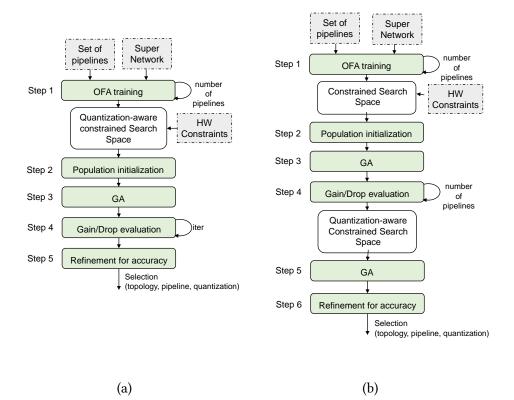

In the following, we present our proposed efficient design exploration strategy, configured as a CNN selection procedure, based on the ALOHA tools described in Section 3.1. It allows us to treat the network topology, the pre-processing scheme, and the quantization level as random variables during the evolution search. The motivation for the combined feature extraction and topology exploration is further explored in Section 3.3.2. We present two different versions of the selection procedure, detailing the general overview provided in the central column of Figure 3.2. We start from a fast and simple one, whose overview is provided in Figure 3.4a and results in an accurate and efficient, but possibly sub-optimal, selection, obtained with a limited design time. Finally, we describe a more complex and accurate version, shown in Figure 3.4b, relying on a more detailed performance evaluation to improve the selection quality.

### 3.2.1 Fast implementation

The Fast implementation of our network selection procedure is defined in Algorithm 1. The inputs are represented by a set PP of pre-processing pipelines and a set of hardware constraints, respectively defining the design space of feature extracting functions and spectrum resolutions, and the limits to memory footprint and execution time, according to the platform specifications.

Figure 3.4: Design steps to be performed in the *Design pruning* and *Training refinement* stages (central column of Figure 3.2), according to the a) fast and b) accurate implementations of the CNN selection procedure.

In Step 1, the one-shot training of the SuperNetwork architecture, SN, through the OFA utility [59] defines a design space N of candidate points. A restricted set denoted as  $N*_c$  results from the application, in Step 2, of the optional set of constraints: admittance into  $N*_c$  is conditioned by the performance evaluation, where quantization up to 4-bit representation is considered for weights and activations independently, to verify the compliance with the maximum allowed memory footprint.

In Step 3, the GA is executed. We consider populations made up of 100 network models, satisfying the hardware constraints, and evolving for  $G_1$ =20 generations. The composition of the new generation is obtained as the 25 most accurate network architectures of the previous one, 50 new candidate design points obtained through random mutation of those best-performing design points, and 25 resulting from parameters crossover. The possible mutations involve the network topology, the input resolution, and the feature extraction. The performance evaluation in this step is based on the one-shot training accuracy.

In Step 4 the optimal model is selected: the simplest design choice results in the selection of the most accurate design point in the last generation explored. Alternatively, the one-shot accuracy can be refined with a sequence of evaluation actions, repeated *iter* times:

- the last generation A<sub>G</sub> is ordered based on the predicted classification accuracy (during the first iteration, such value matches the one-shot accuracy);

- the most accurate CNN architecture is selected for 100 epochs of Detailed training, where data augmentation is applied to reduce the overfitting effect;

- the CNN architecture is quantized according to the selected quantization policy, and retrained for 100 epochs to reduce the accuracy drop;

- retraining gain and quantization drop are evaluated and exploited to improve the predicted accuracy of the architectures in A<sub>G</sub>.

The user can define the number *iter* of iterations, which is most suitable to the effort and compute time that he is willing to dedicate to the selection flow. Values of *iter* different than 1 also require updating the accuracy gain and quantization drop exploited to obtain the predicted accuracy. To provide some examples, gain and drop can be updated by: 1) considering the

Algorithm 1: Fast CNN Architecture selection

```

Input: PP(H, W, AudioProc), SN, hw(Mem, Texe)

Result: CNN architecture a

Step 1. OFA training;

for i \in [1, p] do

| OFA_train(SN, PP_i);

N = \{N(PP_1), ..., N(PP_p)\};

Step 2. Population initialization;

N*_{c} = \{n_{i} | (\operatorname{Mem}^{*}(n_{i}), \operatorname{Texe}(n_{i})) < hw(Mem, Texe)\};

A_1 = \{n_1, ..., n_{100}\} with n_i \in N *_c;

Step 3. GA in HW-aware search space N*_c;

for i \in [1, G] do

Evolution_Search(A_i, N*_c);

A_G;

Step 4. Quantization drop evaluation;

for i \in [1, iter] do

Order(A_G, Accuracy);

Detailed_train(best(A_G));

q(PP_i) = Evaluate_Gain;

Quantization((n, quant));

d(PP_i) = Evaluate_Drop;

Adjust_accuracy(A_G, g(PP_i), d(PP_i));

a = best(A_G);

Step 5. Refinement for Accuracy;

return a

```

values evaluated for the design point with the closest memory footprint; 2) considering an average with the previously evaluated values; 3) considering the last evaluated value.

After the last iteration, Step 5 performs a final refinement on the selected architecture, which can be preceded by the exploration of the optimal learning rate and batch size.

### 3.2.2 Accurate Implementation

The fast procedure introduces the estimation of the effects of quantization on the model's accuracy only during the final selection process. To remedy this flaw, we also developed a more accurate version, described in Algorithm 2.

In this case, the population initialization in Step 2 defines the constrained search space  $N_c$  considering only quantization up to 8 bit, which is the precision targeted by the CMSIS library and typically has very little impact on the network's accuracy. The first run of the GA in Step 3 is exploited as a preliminary step for a more reliable accuracy evaluation, considering refine-

ment with the detailed training and the quantization effect. Following the general assumption that a network with a higher number of parameters can benefit more from the training procedure, we select as the most adequate design points to investigate these effects the CNNs (one for each of the pre-processing pipelines) belonging to  $A_{G_1}$  and having an accuracy within one percentage point from the best one, and the biggest footprint: this analysis is exploited as a prediction model for the networks requiring more aggressive quantization to fit the memory constraint and be included in the search.

Therefore, the retraining gain and quantization drop are evaluated in Step 4. In this implementation, the training time on the Detailed engine has a high impact on the overall exploration time. To limit it, we exploit a *static augmentation* of the training dataset, reducing the time dedicated to pre-processing operations and required to obtain different augmentation effects at each epoch: multiple copies of the dataset, enforcing different random levels of data augmentation, are created, saved and made available for successive training procedures. We found that such a solution does not impact the final accuracy.

In Step 5, the GA is executed for a second time, starting from the last generation  $A_{G_1}$ , produced in Step 3, and including in the new search space,  $N*_c$ , the possibility to perform quantization up to 4 bits. At this point, the ranking of the architectures based on their predicted accuracy takes into account the effects evaluated in Step 4.

After  $G_2$ =20 generations, the most accurate model, associated with its pre-processing and quantization scheme, is chosen as the optimal selection. Step 6 represents the final refinement phase.

#### 3.2.3 Selection time

The required exploration time for the described selection procedures is quantified in Table 3.1, listing the operations performed according to the fast and accurate implementations, based on measurements performed on NVIDIA Tesla T4, exploited for the one-shot training, and on NVIDIA Tesla P100. The exploration time depends on the search parameters, more specifically on the number of different pre-processing pipelines (|PP|) and quantization levels (Q) considered, and on the number of refinement steps performed until selection (*iter*). We report an estimation for each table entry.

Algorithm 2: Accurate CNN Architecture selection

```

Input: PP(H, W, AudioProc), SN, hw(Mem, Texe)

Result: CNN architecture a

Step 1. OFA train;

for i \in [1, p] do

| OFA_train(SN, PP_i);

N = \{N(PP_1), ..., N(PP_p)\};

Step 2. Population initialization;

N_c = \{n_i | (\operatorname{Mem}(n_i), \operatorname{Texe}(n_i)) < hw(Mem, Texe)\};

A_1 = \{n_1, ..., n_{100}\} with n_i \in N_c;

Step 3. GA in HW-aware search space N_c;

for i \in [1, G_1] do

Evolution_Search(A_i, N_c);

A_{G_1};

Step 4. Quantization drop evaluation;

D = \{n_{PP_1}, ..., n_{PP_n}\} where n_{PP_i} has biggest footprint in A_{G_1};

for n \in D do

Detailed_train(n);

g(PP_i) = Evaluate_Gain;

Quantization(n);

d(PP_i) = \text{Evaluate_Drop} = \{d_{x8w8}, d_{x4w8}, d_{x8w4}, d_{x4w4}\};

N*_{c} = \{n_{i} | (\operatorname{Mem}^{*}(n_{i}), \operatorname{Texe}(n_{i})) < hw(Mem, Texe)\};

A'_1 = A_{G_1};

Step 5. GA in HW aware Search Space N*_c;

for i \in [1, G_2] do

Adjust_accuracy(A'_i, g(PP), d(PP));

Evolution_Search(A_i, N*_c);

a = best(A'_{G_2});

Step 6. Refinement for Accuracy;

return a

```

For the use-cases presented in the following, where |PP| = 6 and Q = 4, the Gain/ Drop evaluation requires 51 hours in the accurate implementation, against 3h 30 needed in the fast one with an *iter* choice of 1, which does not scale with the number of pipelines and quantization levels explored. Furthermore, we also mean to emphasize the substantial savings deriving from the CNN topology/ pre-processing co-exploration. A separate evaluation would in effect require repeating the topology GA search on multiple design spaces, as many times as is the number of pipelines considered, or assuming in advance a given scheme, neglecting such an important design variable. This would require 36 hours of GA exploration, against the 6 hours needed by the fast implementation. Thus, the fast implementation allows a factor *PP* reduction of the required exploration time after the one-shot training.

|            | St        | ер        | Executio                  | n Time                |  |

|------------|-----------|-----------|---------------------------|-----------------------|--|

| Operation  | Accurate  | Fast      | Accurate                  | Fast                  |  |

|            | Selection | Selection | Selection                 | Selection             |  |

| OFA train  | 1         | 1         | $2h \ 30 \times  PP $     | $2h \ 30 \times  PP $ |  |

| GA         | 3         | 3         | 6h                        | 6h                    |  |

| Gain eval  | 4         | 4         | 1h 30 $	imes$ $ PP $      | 1h 30 $	imes$ iter    |  |

| Drop eval  | 4         | 4         | $2h \times Q \times  PP $ | 2h 	imes iter         |  |

| GA         | 5         | -         | 6h                        | _                     |  |

| Refinement | 6         | 5         | 5h                        | 5h                    |  |

Table 3.1: Step by step required exploration time for the accurate and fast selection procedure, where the OFA training is executed on NVIDIA Tesla T4, while the GA exploration and the detailed training are executed on NVIDIA Tesla P100.

### 3.3 Experimental Results

We describe in the following the experimental results deriving from the application of the selection procedure, proposed as thesis contribution, to the design of a KWS system, considering two different deployment scenarios defined based on the state of the art [61, 62], enabling a direct comparison with the literature dealing with NAS for the design of KWS applications.

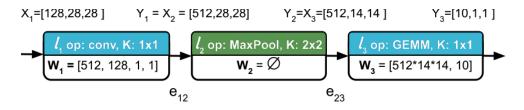

#### 3.3.1 Search Space definition

The composition of the search space is summarized in Table 3.2. Each CNN design point presents either 1 or 2 convolutional stages, separated by a MaxPooling layer and consisting in 1 to *Max Depth* convolutional layers. Column 3 lists the possible channel width values, while Column 4 summarizes the considered kernel sizes, both set independently for each convolutional layer. The possible feature size within each stage is defined in column 5, while column 6 reports the stage's maximum depth. All the network configurations present a final fully connected stage.

As six pre-processing pipelines are considered, as described in Section 3.3.2, the training process at Step 1 of Algorithms 1 and 2 results in a set of over 330000 CNNs available for exploration, corresponding to all the combination of parameters in Table 3.2 and the pre-

| Stage | Operator | Output<br>Features | Kernel<br>Size | Input<br>Size    | Max<br>Depth |

|-------|----------|--------------------|----------------|------------------|--------------|

| 0     | Conv     | 16/32/64           | 3x3/5x5        | 40x32/32x16/16x8 | 1            |

| 1     | Conv     | 16/32/64           | 3x3/5x5        | 20x16/16x8/8x4   | 5            |

Table 3.2: Parameters of the CNN architectures which constitute the Design Space for NAS targeting SensorTile.

processing schemes.

#### 3.3.2 Preliminary Pre-processing exploration

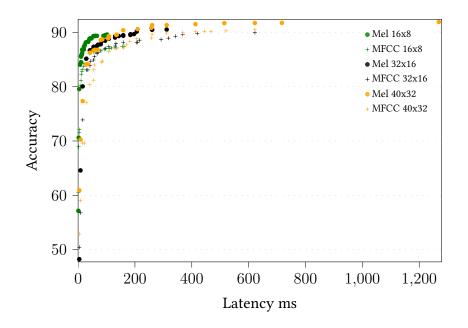

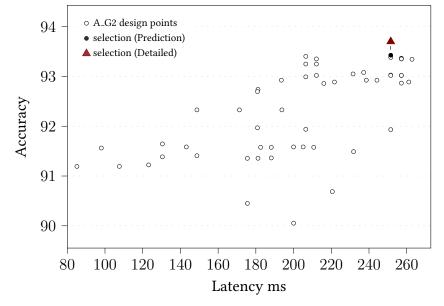

We started our exploration process by estimating the impact of adapting the pre-processing choice to the hardware target, considering the variability of feature preparation choices reported in the literature. We thus compared different feature-extracting functions and the resulting spectrogram's resolutions. Figure 3.5 shows the output of an evolution search conducted on the search space defined in Section 3.3.1, based on a hardware-aware search strategy evolving by optimizing the design points to be Pareto optimal in terms of classification accuracy and inference time on the target platform, estimated with the latency evaluation tool described in Section 3.1. We repeated the search process on six distinct search spaces, each corresponding to a pre-processing scheme choice, exploiting either Mel-spectrogram or MFCC as feature-extracting functions and resulting in 16x8, 32x16, or 40x32 input resolution. Each curve in the figure represents the Pareto fronts obtained after 20 generations, resulting from the different choices of the input resolution and selected feature extracting function. As can be derived from the plot, the overall Pareto front would be made up of design points exploiting different pre-processing schemes: for example, optimal points in the left region are trained on 16x8 Mel-spectrograms, while in the rightmost region of the plot the higher accuracy values are reached thanks to 40x32 spectrograms.

Furthermore, this design choice impacts the overall system performance, as summarized in Table 3.3, reporting the execution time of online pre-processing, measured on the target platform. The measured values do not include the evaluation time of the constant parameters (e.g. the coefficients of the Mel filtering banks, and the DCT matrix), which can be computed

Figure 3.5: Comparison of the Pareto optimal design points resulting from NAS based on distinct evolution searches considering pre-processing schemes based on Mel and MFCC, with input resolutions of 16x8, 32x16, and 40x32.

once at first execution, and memorized for the successive iterations of the audio processing.

Pre-estimating the most suitable pre-processing choice for the target task is thus not trivial. Due to this reason, we consider in the following its co-exploration with the CNN topology and quantization scheme.

| Design Space            | Constraints    | Constraints Reference |  |

|-------------------------|----------------|-----------------------|--|

|                         | MOPS: 20       | [61], referred to as  |  |

| as defined in Table 3.2 | Memory 200kB   | Medium region         |  |

|                         | Latency: 390ms | obtained based on     |  |

|                         |                | model in Figure 3.3   |  |

#### 3.3.3 Use-case 1

Table 3.4: Summary of search parameters for NAS targeting use-case 1.

We first considered as a reference the Medium size region defined in [61], as summarized in Table 3.4, considering a maximum memory footprint of 200 kB and a maximum complexity

|                   | Pre-processing time |

|-------------------|---------------------|

| Mel 16x8          | 46 ms               |

| MFCC 16x8         | 48 ms               |

| Mel 32x16         | 94 ms               |

| <i>MFCC 32x16</i> | 98 ms               |

| Mel 40x32         | 120 ms              |

| <i>MFCC 40x32</i> | 132 ms              |

Table 3.3: Measured execution time for the considered preprocessing schemes on ST Sensor-Tile.

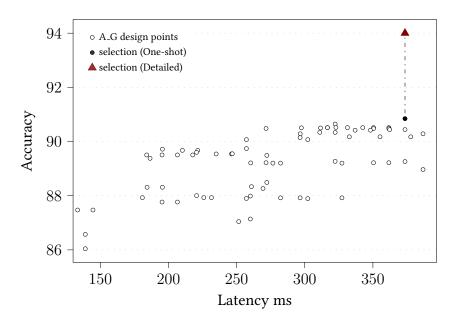

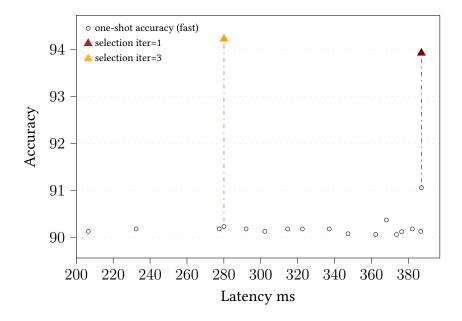

Figure 3.6: Fast selection output in 200kB - 20 MOPS search space. The selected model is highlighted, and its final accuracy upon detailed training is reported.

| Network model  | Accuracy | Latency | MOPS  | Memory |

|----------------|----------|---------|-------|--------|

| CNN M [61]     | 92.2%    | 86.9%   | 86.5% | 99.7%  |

| fast selection | 94%      | 95.8%   | 86.8% | 60%    |

Table 3.5: Performance metrics summary for the selected design point and the reference stateof-the-art network, in the 200kB-20MOPS region, expressed as a percentage of the constraint's value.

of 20 MOPS, translated into a 390ms latency constraint. The output of the fast selection process on the design space resulting from the constraints applied to the search space defined in Section 3.3.1 is reported in Figure 3.6. Every bullet represents a design point selected by the GA to belong to the last generation, and it is placed based on its estimated latency and its one-shot accuracy. The highlighted point represents the selection resulting from an *iter* value equal to 1. The selection output also includes the pre-processing and quantization scheme: 8-bit representation for both weights and activations, and Mel-based pre-processing, resulting in 32x16 input spectrograms. The selected network model is finally retrained on the Detailed engine for 100 epochs, exploiting data augmentation through random shifts and random noise addition, and then quantized, resulting in the refined accuracy reported in the plot. Based on our hyper-parameters exploration, the training exploits a learning rate value lr = 0.025, batch size bs = 16, and SGD optimizer.

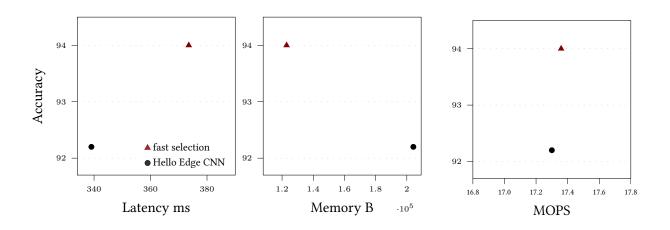

The co-exploration approach allows us to improve the efficiency of the design process, since, as shown in Figure 3.5, the pre-processing scheme's impact on performance is deeply connected with the search constraints, and consequently to the CNN architecture to be deployed. Thus, as anticipated in section 3.2.3, performing a dedicated preliminary analysis is not only time-consuming but also very complex, especially when multiple constraints need to be considered. As shown in Figure 3.9, the selected architecture reaches 94% accuracy, improving the state-of-the-art CNN model obtained in [61] by up to 1.8% with 40% lower storage requirements, while the number of OPS is increased by 0.3% and results in a 10% higher latency. The exploration summary is reported in Table 3.5. The search process requires around 30 hours, considering 15 hours of one-shot training executed on NVIDIA Tesla T4 GPU, while the GA and the Detailed training were executed on NVIDIA Tesla P100 GPU.

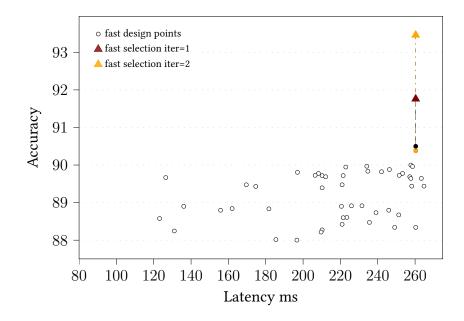

Figure 3.7: CNN architecture fast selection output in 75.7kB - 13.6 MOPS search space. The network models selected based on different choices for the *iter* value are highlighted.

| Design Space            | Constraints    | Constraints Reference |  |

|-------------------------|----------------|-----------------------|--|

|                         | MOPS: 13.6     | [62], parameters of   |  |

| as defined in Table 3.2 | Memory 75.7kB  | the selected network  |  |

|                         | Latency: 265ms | obtained based on     |  |

|                         |                | model in Figure 3.3   |  |

#### 3.3.4 Use-case 2.

Table 3.6: Summary of search parameters for NAS targeting use-case 2.

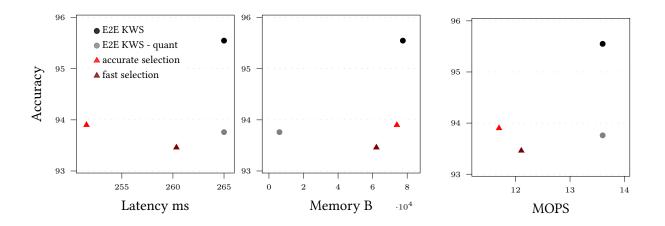

As a second use-case, we considered as a reference the work of [62], exploiting the number of OPS and the storage requirements stated for their presented network as the constraints to define the search space. The search parameters are summarized in Table 3.6. The reference CNN model achieves 95.55% accuracy, while its quantized version, exploiting mixed data representation (2.91 bits to represent activations and 2.51 bits to represent weights) reaches 93.76% accuracy.

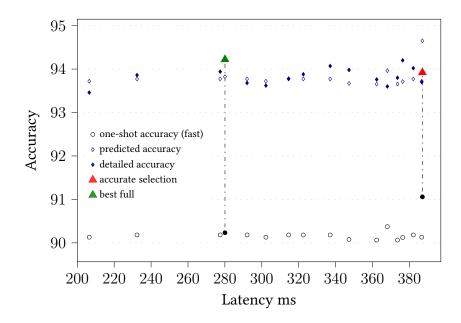

Figure 3.7 shows the output of the fast selection procedure, reporting two possible selections corresponding to iter = 1 and iter = 2 values. As can be derived from the plot, the

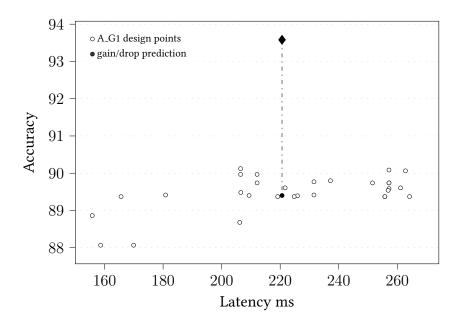

(a) Pareto plot of the pruned design space after Step 3. The model exploited for the accuracy gain/drop evaluation, on a pipeline based on Mel with 32x16 input resolution, is highlighted.

(b) Pareto plot of the pruned design space after Step 5. The comparison between the predicted and training accuracy on the final selection is highlighted.

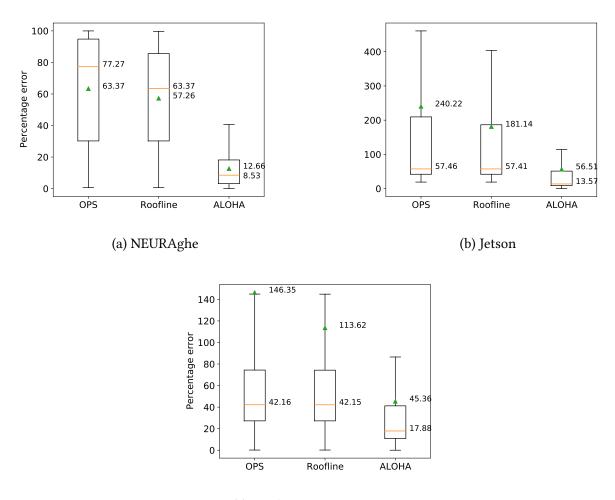

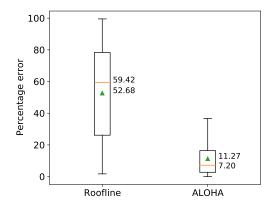

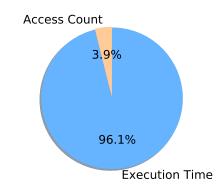

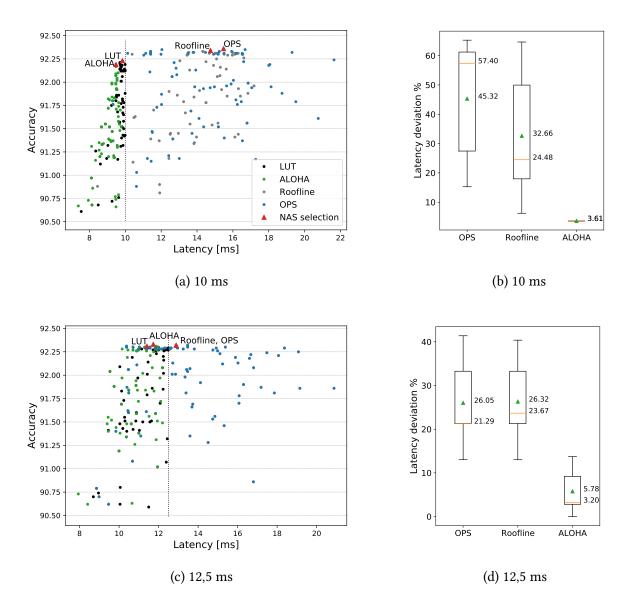

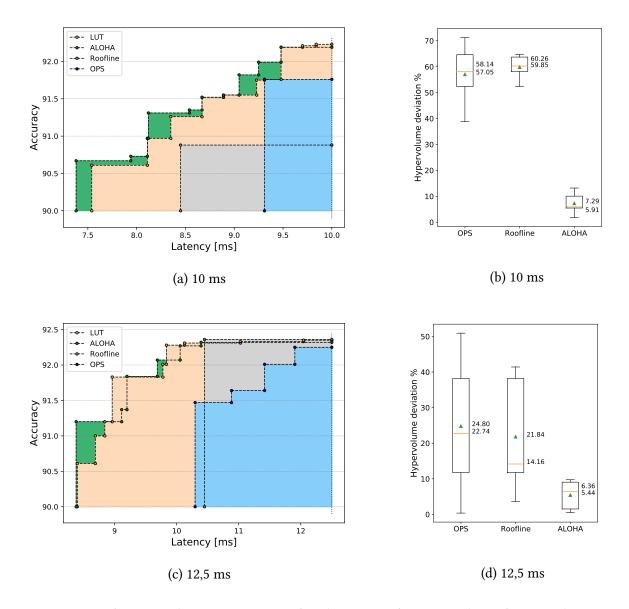

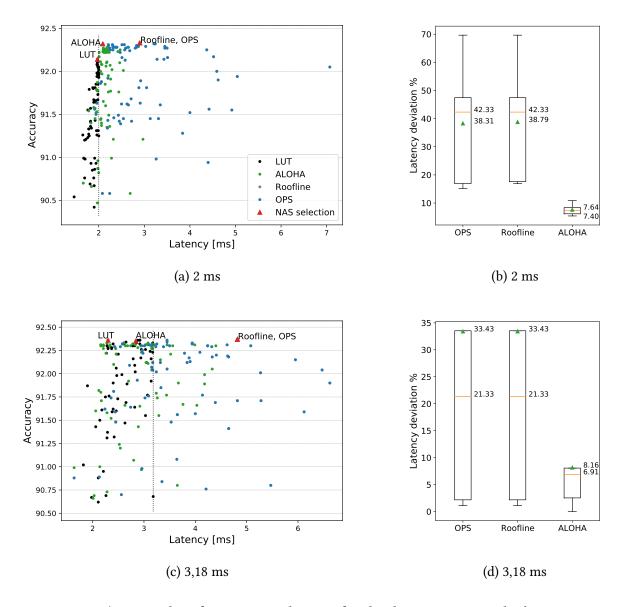

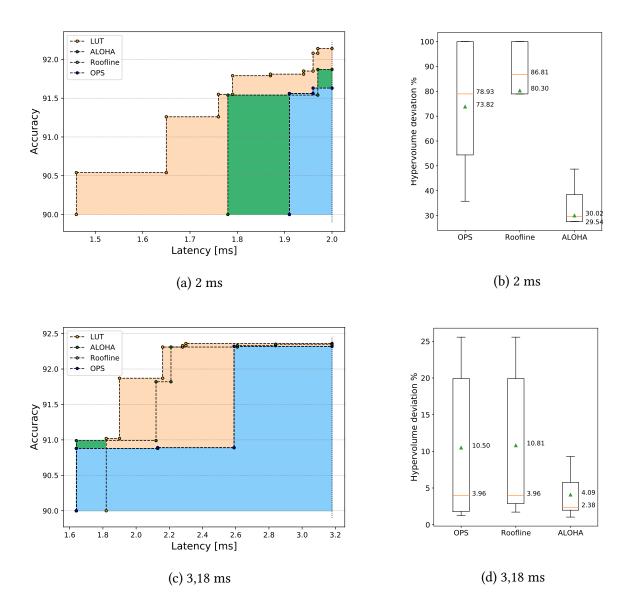

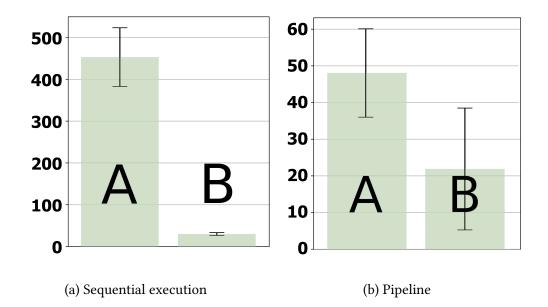

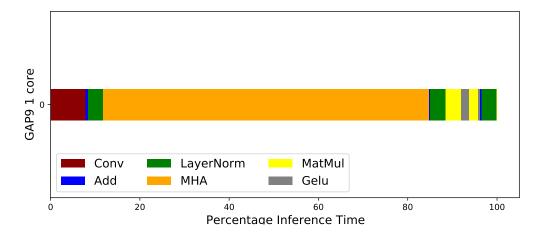

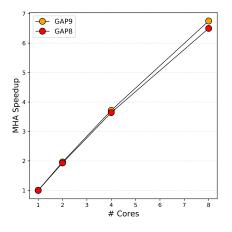

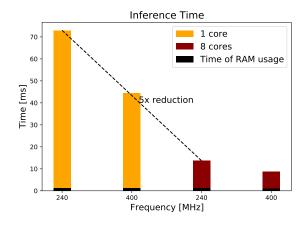

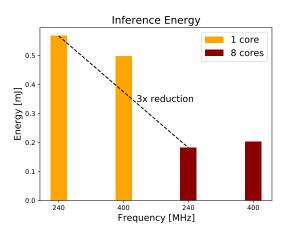

Figure 3.8: Accurate selection procedure in 75.7kB - 13.6 MOPS search space.