# UNIVERSITÀ DEGLI STUDI DI CAGLIARI FACOLTÀ DI INGEGNERIA

# Dottorato di Ricerca in Ingegneria Elettronica e Informatica (Anno Accademico 2007-2008 - XX ciclo)

# DESIGN AND OPTIMIZATION TECHNIQUES FOR VLSI NETWORK ON CHIP ARCHITECTURES

A NOVEL COMPLETE DESIGN FLOW FOR APPLICATION SPECIFIC NOCS

PhD thesis by: Paolo Meloni

# Contents

|          | Inti | roduction                                                 | ix |

|----------|------|-----------------------------------------------------------|----|

| 1        | Cor  | ntext and Motivation                                      | 15 |

|          | 1.1  | Introduction                                              | 15 |

|          | 1.2  | SoC paradigm                                              | 15 |

|          | 1.3  | MPSoC paradigm                                            | 16 |

|          | 1.4  | Challenges of Deep Sub-Micron Technologies                | 17 |

|          |      | 1.4.1 Complexity of the interconnect hierarchy            | 18 |

|          |      | 1.4.2 Interconnect delay                                  | 18 |

|          |      | 1.4.3 Energy consumption                                  | 19 |

|          |      | 1.4.4 Interconnect reliability                            | 20 |

|          |      | 1.4.5 Process variations                                  | 20 |

|          |      | 1.4.6 Complexity of interconnect modeling                 | 20 |

|          | 1.5  | Interconnect architecture optimization:                   |    |

|          |      | motivation                                                | 21 |

|          |      | 1.5.1 Network-on-chip communication architectures         | 22 |

|          | 1.6  | Network-on-chip architectures features and classification | 23 |

|          |      | 1.6.1 Network design constraints                          | 24 |

|          | 1.7  | Network-on-chip architecture design space                 | 26 |

|          |      | 1.7.1 Fundamental network parameters                      | 26 |

|          |      | 1.7.2 Network Design Decisions                            | 31 |

|          | 1.8  | State of the Art NoC Architectures                        | 33 |

|          |      | 1.8.1 AMBA Shared Bus                                     | 36 |

|          |      | 1.8.2 AMBA Multi-Layer                                    | 37 |

|          |      | 1.8.3 ×pipes NoC                                          | 37 |

| <b>2</b> | Cor  | mparative analysis of NoCs and Traditional Interconnects  | 41 |

|          | 2.1  | Related Work                                              | 42 |

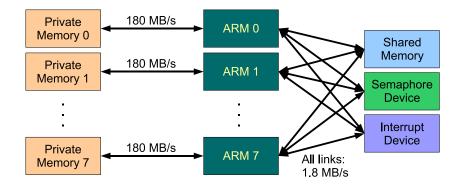

|          | 2.2  | The Fabrics Under Test                                    | 43 |

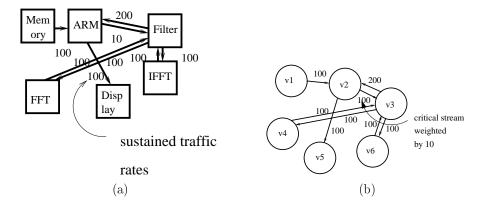

|          | 2.3  | The Test Applications                                     | 45 |

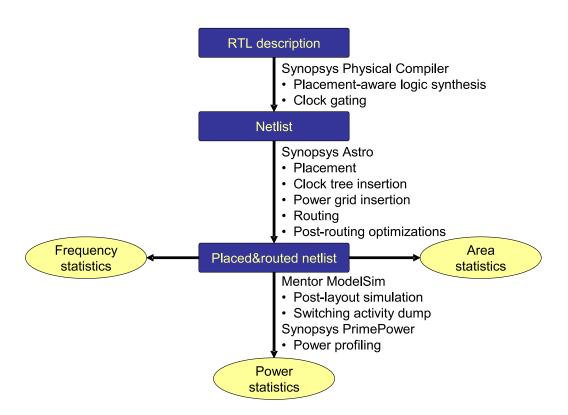

|          | 2.4  | Reference Characterization Flow                           | 48 |

iv CONTENTS

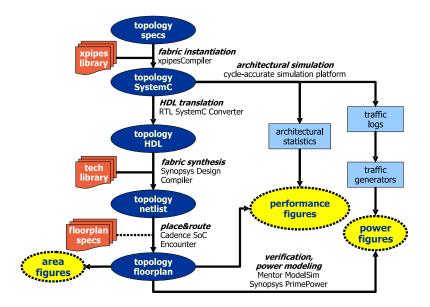

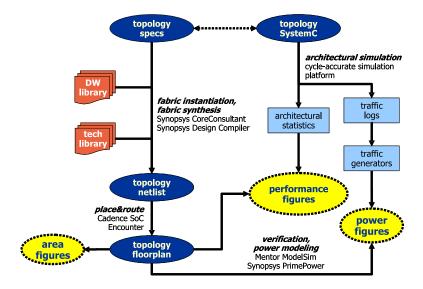

|   |     | 2.4.1        | Fabric Simulation                                   | 18  |

|---|-----|--------------|-----------------------------------------------------|-----|

|   |     | 2.4.2        | Fabric Synthesis                                    | 19  |

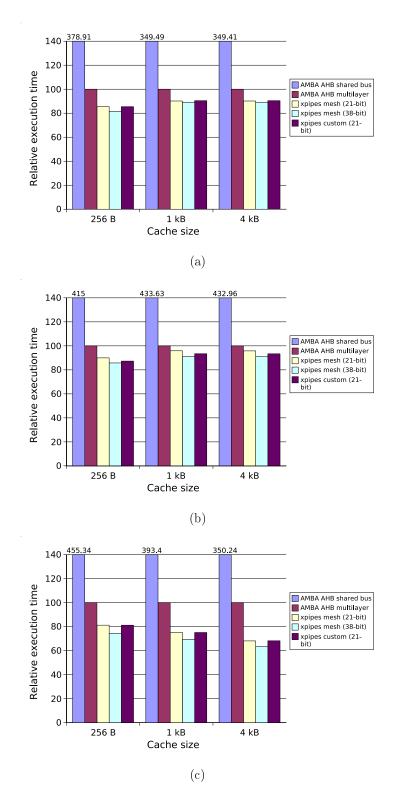

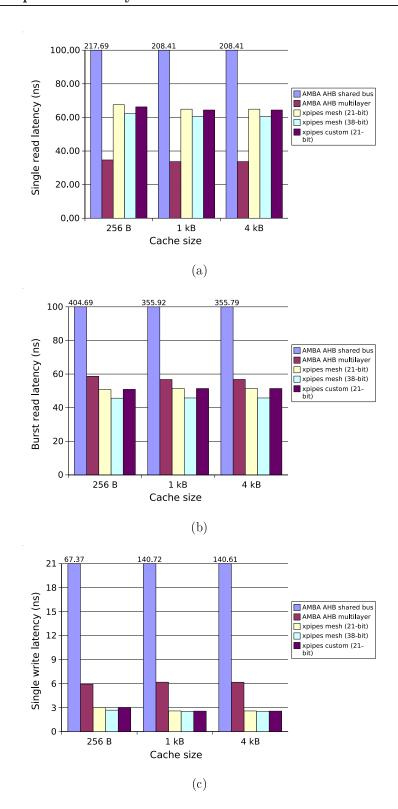

|   | 2.5 | Perfor       |                                                     | 53  |

|   |     | 2.5.1        | Interconnect Performance                            | 53  |

|   |     | 2.5.2        | Interconnect Area, Frequency of Operation and Band- |     |

|   |     |              | width                                               | 56  |

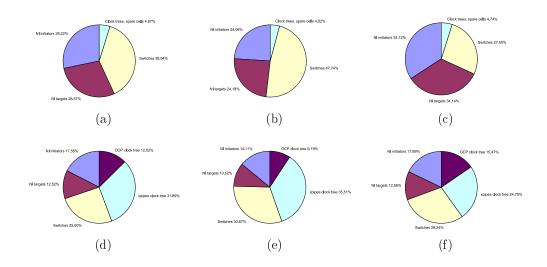

|   |     | 2.5.3        | Interconnect Power and Energy                       | 58  |

|   |     | 2.5.4        | Split Analysis of Area and Power Contributions 6    | 31  |

| 3 | Des | igning       | Application-Specific Networks on Chips 6            | 39  |

|   | 3.1 | Introd       | $egin{array}{cccccccccccccccccccccccccccccccccccc$  | 36  |

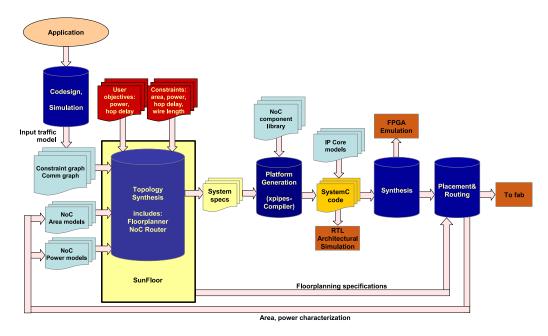

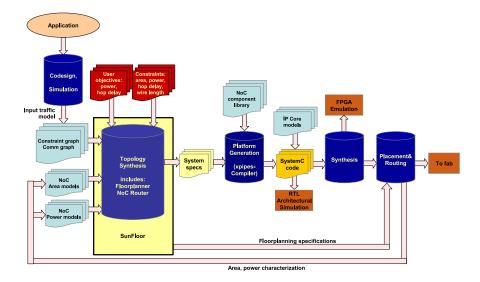

|   | 3.2 | Design       | n Flow                                              | 71  |

|   | 3.3 | Input        | Models                                              | 75  |

|   | 3.4 | Design       | n Algorithms                                        | 76  |

|   | 3.5 | Exper        | iments and Case Studies                             | 33  |

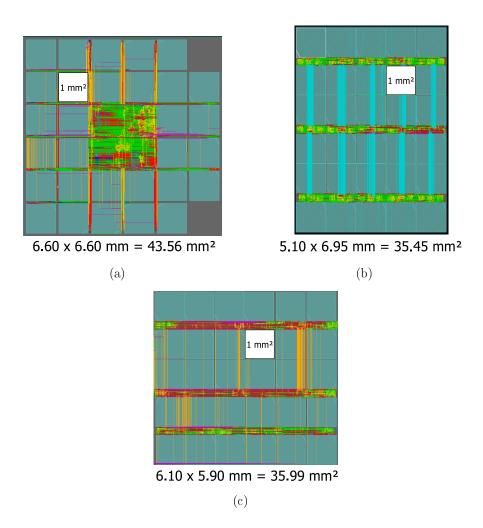

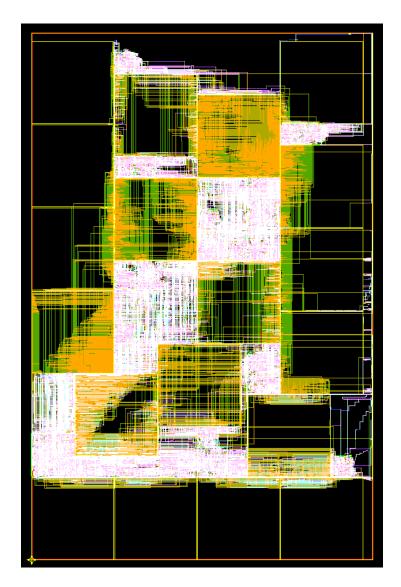

|   |     | 3.5.1        | Layout-level Comparisons                            | 33  |

|   |     | 3.5.2        | Experiments on SoC Benchmarks                       | 35  |

| 4 | Are | a and i      | Power Modeling for Networks-on-Chip components &    | 9:  |

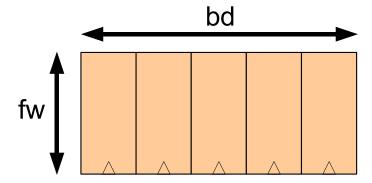

|   | 4.1 | The $\times$ | cpipes Switch Architecture                          | ) 4 |

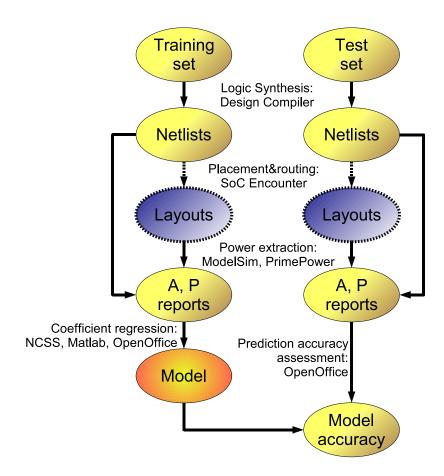

|   | 4.2 | Propo        | sed Modeling Methodology                            | ) 4 |

|   |     | 4.2.1        | Parameters of Interest                              | )(  |

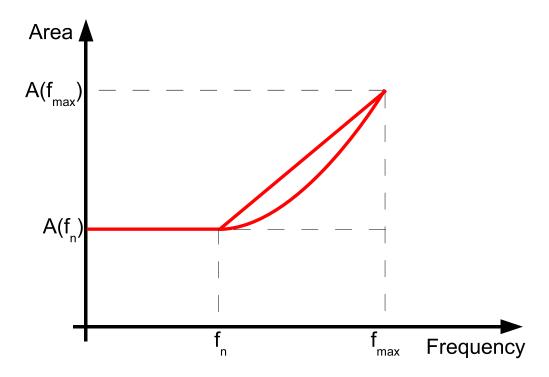

|   |     | 4.2.2        | Area and Power Models                               | 3(  |

|   |     | 4.2.3        | Choice of a Relevant Training Set                   | )3  |

|   |     | 4.2.4        | Fitting Model Coefficients                          | ) 4 |

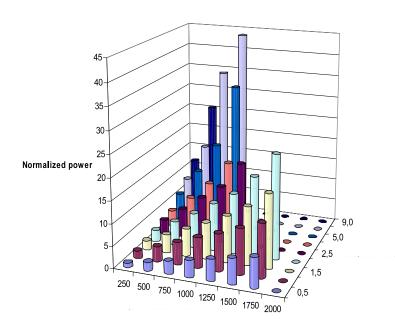

|   | 4.3 | Exper        | imental Results                                     | )6  |

|   |     | 4.3.1        | Experiments with Netlist-Based Models and a         |     |

|   |     |              | Netlist-Level Test Set                              | 7 ( |

|   |     | 4.3.2        | Test Case: a Complete NoC Topology                  | )8  |

|   |     | 4.3.3        | Experiments with Netlist-Based Models and a         |     |

|   |     |              | Layout-Level Test Set                               | )8  |

|   |     | 4.3.4        | Experiments with Layout-Based Models and a          |     |

|   |     |              | Layout-Level Test Set                               | L 1 |

|   |     | 4.3.5        | Experiments with a Parabolic Model for the Depen-   |     |

|   |     |              | dency on the Target Synthesis Frequency             | 13  |

| 5 | Rot | uting P      | Aware Switch Hardware Customization 11              | . 7 |

|   | 5.1 |              | luction                                             |     |

|   | 5.2 | Refere       | ence design flow                                    | L8  |

|   | 5.3 | Routi        | ng aware hardware optimization                      | T 6 |

|   |     | 5.3.1        | Hardware-Level Customization Support                | 21  |

CONTENTS v

|   |      | 5.3.2  | Software-Level Customization Support        |

|---|------|--------|---------------------------------------------|

|   | 5.4  | Custo  | mization method effectiveness evaluation    |

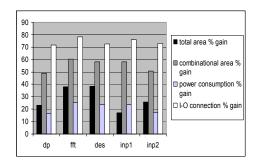

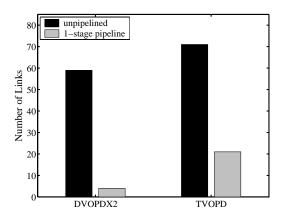

|   |      | 5.4.1  | Experiments on the Multimedia benchmark 122 |

|   |      | 5.4.2  | Experiments on SoC benchmarks               |

| 6 | 65 r | ım No  | C Design 129                                |

|   | 6.1  | NoC I  | Design Flow                                 |

|   |      | 6.1.1  |                                             |

|   |      | 6.1.2  | Post-Layout Analysis                        |

|   | 6.2  |        | Design in 65 nm Technologies                |

|   |      | 6.2.1  |                                             |

|   | 6.3  | Exper  | imental Results                             |

|   |      | 6.3.1  | Technology Scaling from 90 to 65 nm         |

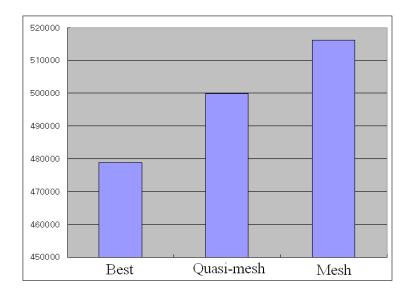

|   |      | 6.3.2  | Topology design                             |

|   |      | 6.3.3  | High Bandwidth Application                  |

|   |      | 6.3.4  | Effect of Link Pipelining                   |

|   |      | 6.3.5  | Low Bandwidth Application                   |

| 7 | Con  | clusio | ns 149                                      |

|   | List | of fig | ures 155                                    |

|   | List | of tak | oles 157                                    |

# Introduction

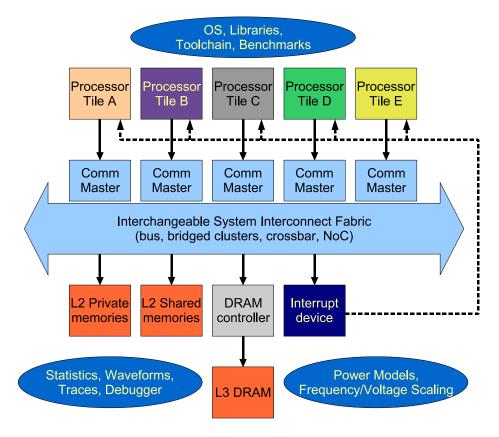

As steady progress is being made in the miniaturization of chip features. embedded systems are quickly evolving towards complex devices, including a large set of computation engines, dedicated accelerators, input/output controllers and multiple memory buffers. MultiProcessor System-on-Chip (MP-SoC) is a commonly used term to describe the resulting outcome. However, this feature- and performance-oriented evolution is not devoid of significant challenges, including mastering the increasing design complexity and minimizing power consumption. Moreover, miniaturization itself is bringing its own set of design issues at the physical level, originated primarily by an increasing ratio of wire vs. logic propagation delay. One of the most critical areas of MPSoC design is the interconnect subsystem, due to architectural and physical scalability concerns. The former is due to the performance pressure associated with several system cores that simultaneously demand communication resources, and subsequently relates to the need for providing adequate bandwidth and latency. The latter is due to the intrinsic issues due to the design of wires that must span across the whole chip area, namely, propagation delay, noise and rosstalk. Traditional shared bus interconnects are relatively easy to design, but do not scale well. Thus, evolutions have been conceived both from the protocol (e.g. outstanding transactions with outof-order delivery) and the topology (e.g. bridges, crossbars) points of view. Nevertheless, scalability is still suboptimal, as protocol improvements still hit a bandwidth limit due to the available physical resources, and topological extensions require the use of bridges (i.e. multiple buses or "spaghetti-like" design) or large area overheads in routing structures (i.e. using crossbars). Networks-on-Chip (NoCs) have been suggested as a promising solution to the scalability problem. By bringing packet-based communication paradigms to the on-chip domain, NoCs address many of the issues of interconnect fabric design. Wire lengths can be controlled by matching network topology with physical constraints and bandwidth can be boosted by increasing the number of links and switches. This thesis focuses on the design and the optimization of Network on Chip architectures paying special attention to the aspects rex Introduction

lated to the relationship between the system level design decisions and the back-end implementation variables. In particular, the core of the presented research work is a complete flow for application-specific NoC design. The proposed flow helps the NoC designer to perform all the design actions required, from the target application task graph to the placement&routing steps. The activities concerning this research have been performed in collaboration with three external partners:

- Università di Bologna

- Stanford University

- Ecole Polytechnique Fédérale de Lausanne

As will be explained more in detail in the thesis, the proposed flow aims to tailor the optimal NoC structure for a given application. The flow consists of a front-end part, devoted to the synthesis of the optimal NoC configuration based on the application communication requirements, of a back-end part, in charge of the implementation (down to the layout level) of the configuration chosen by the front-end, and of some side steps needed to produce the information received in input by the previously mentioned two parts and to close the gaps between them. In the first chapter, the motivation bringing to approach to this research field is dissussed. In this aim, an overview of the landscape of todays multicore systems implemented on a single chip is included, to explain why, from a functional point of view, modern computing devices would require a new interconnection architecture paradigm. Moreover, the problems related to the physical aspects, such as scalability, design feasibility and reliability, that emerge with the technology shrinking and pose the need for a more scalable and structured communication infrastructure, are discussed. Once this context is illustrated, some exemples of state of the art interconnection systems are presented. A brief summary about most efficient and diffused bus-bases systems and about the best known on-chip networks is reported. ×pipes, an in-house developed Network on Chip architecture, conceived in 2002 and so far defined in a completely reconfigurable and synthesizable RTL component library, is depicted more in detail, being the reference architecture for the whole research work and for the whole presented design flow. In the second chapter, to assess the usefulness of NoC architectures, and to figure out the advantages related to them, a thorough comparison between bus-based systems (simple and complex) and on-chip network is presented. A great number of design variables affect the result of such a comparison. However, to make the analysis meaningful, there are aspects which cannot be ignored. As mentioned above, it is not possible to just

Introduction xi

simulate each architecture to assess its effectiveness. Even if performance alone is taken into account, the clock frequency variable can skew results. Further, since interconnects by definition span across significant portions of the die, wiring congestion and wire propagation delays are very difficult to estimate in advance. Therefore, the overhead of crossbars and NoCs can only be fully understood after having mapped the architecture onto a chip layout. A shared-bus, a crossbar and a NoC designs were brought to the chip layout level in order to highlight the respective strengths and weaknesses in terms of performance, area and power, keeping an eye on future scalability. Inside this chapter, the back-end part of the proposed NoC design flow is introduced and illustrated in detail. Moreover, it is used to take the test platforms down to a placed&routed layout, in order to get frequency, area and power figures. A 0.13  $\mu m$  library was used for this study. In the third chapter, the whole flow for application-specific NoC design is presented. A preliminary description of the reasons pushing to the approach to application-driven design is given, then the different steps of the proposed flow are commented in detail. In particular, the front-end part related to the high-level topology synthesis is illustrated as reference and how its interfacing with the back-end part of the flow was allowed is explained. Moreover, the chapter includes the comment related to a set of experiments proving the usefulness of the proposed approach and the consistence of the used design methods. In the fourth chapter, one of the most important side steps included in the flow is presented. This step is represented by the construction of detailed area and power models, needed by the front-end of the flow to evaluate the impact of each decision taken with respect to the chosen network configuration. The models are derived by using information and experimental results coming from the back-end part of the flow, and are thus mandatory to close the gap between the configuration synthesis and the actual results after implementation. A complete methodology extendible to xpipes as well as to other NoC architectures is presented and tested to asses accuracy and effort required. In the fifth chapter, an original design implementation technique, aimed to reduce the hardware overhead introduced by NoC components is briefly explained. Basically, according to this technique the internal hardware of the xpipes NoC router is specifically reduced to the minimum configuration needed to suit the traffic required by a given application. The proposed technique is completely integrated in the xpipes design flow. Finally, in the sixth chapter, the NoC design is investigated referring to Deep Sub Micron techology. Athough the scalability and predictability improvements, derived by the new communication paradigm, could already be assessed by evaluating the experiments commented in Chapter 1, further experiments and implementation trials have been performed referring to smaller technologies, xii Introduction

namely 90 nm and 65 nm, to assess actual NoC feasibility and efficiency in challenging technology nodes. Moreover the evaluation of real impact of wiring capacitance, was tackled thoroughly shedding light on a major important point in NoC research. Updates to the proposed design flow were found out to be mandatory in such a contest, allowing to define some very useful guidelines for the NoC designer.

# Chapter 1

# Context and Motivation

#### 1.1 Introduction

Modern trends in electronics and challenges related to the physical features of future technology processes, bring the need for a scalable and efficient interconnect structure, to support the interaction between the units inside a chip. SoC and MPSoC paradigms, every day more widely diffused, pose strict requirements in terms of functional scalability and reusability of the modules. Moreover, manufacturing with deep sub-micron (DSM) technologies, the designer can not keep up with physical scalability and reliability using classic interconnect structures. So, to introduce the thesis, in this chapter, an overview of the concepts related to modern design paradigms [10] and a brief summary of the physical problems exposed by the technology scaling are reported.

# 1.2 SoC paradigm

By the end of the decade, according to the International Technology Roadmap for Semiconductors [1], it will be possible to realize inside a single silicon die up to 4 billion transistors smaller than 50-nm, operating below one volt and running at 10 GHz. On the other hand, today's market pushes the hardware designers asking for the possibility to run very complex applications, showing the needs for computing devices providing every day higher performances. Network processors used in high-performance routers, handsheld devices merging telephony and multimedia capabilities, digital televisions and set-top boxes, video game stations rendering gaming action in real time, sensor networks, servers, are typical modern devices needed to support performance-hungry applications. A System-on-chip is the result of the inte-

gration of complete complex systems on a single chip. Systems-on-chip use the huge integration capabilities provided by modern technology nodes, mixing in the chip digital, analog, mixed-signal and radio-frequency functions, to find a solution to the challenging design problems in the telecommunications, multimedia and consumer electronics domains. The typical SoC hardware implementation is based on a platform obtained by the composition of a set of independent tiles. A tile is defined as an independent subsystem of the System on Chip architecture that can accomplish a high-level function. It can combine storage, computation and communication interfaces with the system environment. It can be a processing unit (including its cache memory), like a General Purpose Processor (GPP) or a Digital Signal Processor (DSP), a Coarse Grain Architecture (CGA), an Application Specific Integrated Circuit (ASIC), a RAM blocks or an input/output interface. Tiles are also known as Intellectual Property cores (IP cores), typically when designed by another party and later integrated into a SoC platform. Major IP vendors like ARM license their IP cores to platform integrators. The IP cores can be provided in soft form (soft IPs), i.e. their description in a HDL language or a standard-cell netlist is delivered, or in hard form (hard IPs), meaning that a layout level black box is released to be integrated inside the SoC flooplan. Hard IPs can have various sizes and aspect ratios. The possibility to easily integrate inside a platform third party macros is mandatory to take profit about the advantages coming from the improved computing potential, since time-to-market pressure is every day stronger and a complete full-custom design flow of the whole platform is unfeasible.

# 1.3 MPSoC paradigm

Most current SoCs are Multi-Processors SoCs (MPSoCs). They contain multiple instruction-set processors (CPUs), and are seen as the only way to meet future system feature set, design cost, power, and performance requirements. State of the art MPSoCs are processor arrays, instantiating multiple parallel general-purpose processors (GPPs) and multiple application-specific processors (ASPs). They allow to exploit the intrinsic parallelism that is usually present in modern application domains, outperforming in this cases single high-end general purpose processor. Moreover, integrating different processors inside a chip, allows the cores to work at a lower frequency and provide balance between performance and power consumption showing much lower power consumption per core. It is also possible for the designer to specify for each core a different specialized instruction set, bringing the system to a better efficiency and to higher performances. A very useful possibility of-

fered by the MPSoC paradigm is related to accelerating the design process. An MPSoC platform can be easily upgraded or customized for different customer's needs relying on the reusability of the tile or on the integration of third party IPs. This allows to avoid the optimization process for a full-custom designed high end processor, that usually requires extremely long design cycles. MPSoC platform based design flow reduces the gap between the design productivity and the potential offered by future silicon technologies and thus permit to better underly to the time-to-market tremendous pressure. Typical examples of high performance MPSoC are:

- the Cell processor platform designed by Sony, Toshiba and IBM, that is based on one general purpose processor (IBM Power PC) and 8 graphical co-processors (see figure 1.4). The platform will be used for the Playstation 3 game console, high definition television sets and computer servers.

- Niagara 2 platform designed by Sun, including 8-core (look for figure)

- Barcelona designed by AMD, including 4 cores (look for figure)

- DSP PC205 by picoChip, including 1 GPP core and 248 individual ASPs (look for figure)

- Cisco Silicon Packet Processor, including 188 programmable 32-bit RISC processors executing 47 billion instructions per second (BIPS) (look for figure)

- Intel Network Processor, including 1 GPP Core and 16 ASPs (look for figure)

Probably the most advanced research project in the field of high performances MPSoC is Intel's TeraFlop chip including 80 GPPs, interconnected by a mesh-like network-on-chip.

# 1.4 Challenges of Deep Sub-Micron Technologies

Transistor size is constantly reduced in every transition to a new technology node. The minimum feature size, that is the minimal distance separating two wires, can be considered as a common unit for measuring transistor size relative to a given technology. As it became smaller than 90 nm, microelectronics has entered a new era of design challenges called the Deep Sub-Micron

era, mainly characterized by the fact that communication will become more critical than computation. Interconnect will become the dominating factor determining speed, noise and power. Compared to transistors, interconnect has evolved very slowly since CMOS technology has been introduced. In the past thirty years, the wire delay has been reduced by a factor 60 while during the same time for transistors, a factor 1000 has been reached. While, so far, interconnect has never been a critical issue as transistors were dominating the delay [8], in the coming years, interconnect will have to dramatically improve if microelectronics industry wants to keep up following Moore's law [11].

Deep Sub-Micron technologies come up with many challenges mainly affecting the global wire interconnect:

- increasing complexity of the wiring hierarchy

- increasing interconnect delay

- increasing energy consumption

- decreasing interconnect reliability

- increasing process variations

- increasing complexity of the interconnect modeling

## 1.4.1 Complexity of the interconnect hierarchy

The number of metallization levels costantly grows in future DSM designs as interconnect is becoming more and more heterogeneous. The hierarchy complexity must bu managed coherently on the physical plane, considering the distinction between local, intermediate and global interconnect, and on the logical plane, using different solutions to tackle local on-chip communication-architecture, targeting intra-tile communications, or global on-chip communication architecture, targeting inter-tile communications.

# 1.4.2 Interconnect delay

As technology scales down, local and intermediate wires become shorter in average, leading, together with the introduction of new materials, to a dramatic improvement in local and intermediate wire delay. However, many phenomena are deteriorating wire RC delay improvement, affecting the wire resistance (skin effect, effective resistivity, inelastic scattering at the boundaries, process variations...) or the wire capacitance (cross-talk, fringing capacitance,...). Transistor gates become smaller, leading to lower transistor

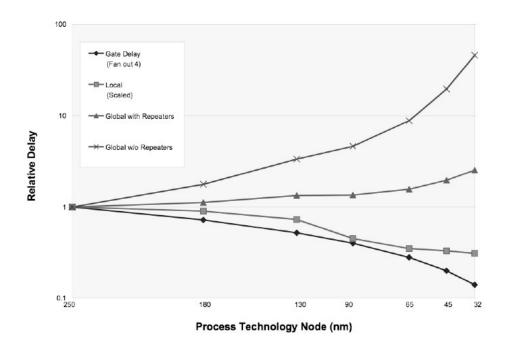

energy consumption and delay. The ratio between gate delay and local wire delay remains about the same. While local wire lengths scale with the technology, global do not. The length of the longest global wires remains about the same as technology scales or could even increase as silicon dies could become larger. So, the relative contribution of the global interconnect to the power consumption and delay increases considerably (see figure 1.1 [1]).

Figure 1.1: Comparison between gate delay and local/global interconnect delay:local wires and gate delay are scaling down while the relative contribution of the global wire delay is increasing with technology

# 1.4.3 Energy consumption

Energy consumption is a critical issue for hand-held devices as battery life is very limited and heat dissipation systems are already reaching their limits. The power consumption of a CMOS circuit has two components: dynamic and static. Dynamic power consumption occurs when a gate is switching from one state to another. Static power consumption is due to the existence of small leakage currents that flow through transistors in cut-off mode. As the industry is moving to Deep Sub Micron technologies, leakage power consumption of CMOS circuits starts to can not be neglected [9]. Leakage current of one transistors is indeed negligible in absolute but as transistors density

is reaching billions of transistors per chip, sub-threshold leakage becomes a major problem, also taking into account its temperature dependence.

## 1.4.4 Interconnect reliability

In Deep Sub-Micron technologies, an interconnect wire cannot be considered as an ideal transmission medium anymore. Signal reliability is affected by inter-wire noise, due especially to the capacitive crosstalk that arises from the reduction of the insulator thickness between wires and the increasing of their aspect ratio, the mutual coupling capacitance increases considerably. Moreover, noise margin is decreased due to power supply and threshold voltage scaling. Crosstalk implies delay degradation and unpredictability. On the other hand wire reliability is deeply affected by electromigration, that occurs when the metal ions in a wire are repeatedly impacted by electrons and thus transported. It causes open-circuit in the wire or short circuit between wires.

#### 1.4.5 Process variations

As minimum feature size becomes smaller than 100nm, systematic or random process differences can arise between dies (inter-die variations) or within one die (intra-die variations). While systematic process variations can be handled by designers, random process variations remain a critical research issue at present time. Process variations may lead to manufacturing yield problems or to time-dependent variations that only appear during the chip operating time and they can either affect the functionality of the system component or only its characteristics. Examples of causes of variations are:

- Variant dopant concentration: this implies voltage threshold variations;

- Limited resolution of lithography: this causes transistor length variations resulting in leakage current variation;

- Line edge roughness problems: edges of the wires are more and more difficult to control as technology scales;

- EDA tool inaccuracies: the technological models integrated in the EDA tools have limited accuracy which introduces variability on system characteristics;

# 1.4.6 Complexity of interconnect modeling

To evaluate delay and power consumption, interconnect used to be modeled as simple RC lumped circuits. However, in Deep Sub-Micron technologies

and especially for long lines like global wires, line resistance will not be negligible anymore compared to driver resistance. Thus, modeling the interconnect will become more complex as models will have to take into account the distributive character of the interconnect. Inductance contributions also have to be taken into account for high performance designs. For very long high performance interconnect (clocked at 1GHz), only transmission line models give accurate results.

# 1.5 Interconnect architecture optimization: motivation

Interconnect is becoming critical in SoC designs due to both system-level and technological constraints. Major factors thus motivate the need for an optimized communication architecture:

- the increasing density of on-chip components which makes past interconnect solutions inefficient

- the need for communication architecture reusability to cope with platformbased design methodology

- the need to tackle problems imposed by DSM technologies effects

SoC design is now moving from computation to communication centric [2], [7]. Communication and data-access are indeed becoming the two most critical issues for future SoC designs. Traditionally, SoC designers have used either ad-hoc wiring or simple shared bus architectures as the global communication architectures. Those solutions were well adapted for small SoC platforms for which interconnect was far less important than computing architectures. However, as the system complexity grows and the wiring delay surpasses the gate delay, those communication architecture, under the load of multiple high-speed processing elements, rapidly become a bottleneck. Designers have been successfully tackling the issue by incrementally improving the bus paradigm. Approaches range from more advanced protocols [17], which keep the shared bus topology but add sophisticated features, like the support for multiple outstanding transactions, to new topological concepts [4, 14, 16], up to the extreme concept of a full crossbar interconnect. These alternatives exhibit varying levels of complexity, performance and reusability. Still, the scalability challenge is not over. A crossbar-based design guarantees maximum bandwidth, but large crossbars run into spaghetti wiring issues, which hinder the achievable frequency of operation and pose severe physical design

problems. Further, large crossbars are expensive to implement. Therefore, for big designs, hierarchical approaches are typically taken; IP cores are glued together by a mixture of buses, crossbars, bridges, decoders and adapters. This choice keeps hardware cost at an acceptable level, but is difficult to design, validate, maintain and extend; and most importantly, it does not really provide a comprehensive answer to the scalability dilemma. In search of a proven solution to scalability worries, researchers turned to wide area networks to get inspiration.

#### 1.5.1 Network-on-chip communication architectures

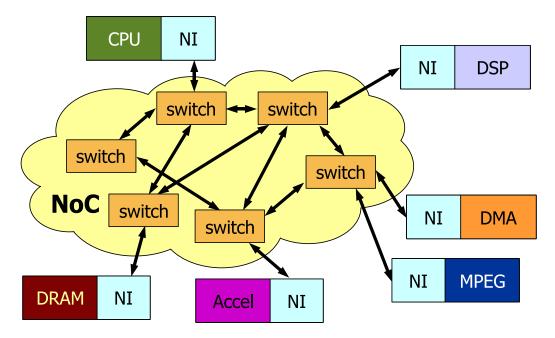

Networks-on-Chip (NoCs) are the target of the design and optimization techinques proposed in this thesis. NoCs were proposed as a scalable solutions to the problems related to the utilization of shared structures in complex SoCs [5, 6]. NoCs (Fig. 1.2) are the on-chip transposition of the packet-switched paradigm; as such, they feature some known properties, but a mostly unexplored set of design tradeoffs. For example, in wide area networks, switches can leverage a whole dedicated chip and a large amount of buffer memory. Within a chip, a switch has to fit within fractions of  $mm^2$  and its power consumption should be some milliwatts at most. The most effective way to implement a switch while staying within those bounds has not been clearly determined yet. Similarly, wide area networks can afford processing latencies of hundreds of milliseconds without problems, while in a NoC an excessive latency overhead for packetization and multi-hop routing could severely affect area, power and latency metrics.

Provided that designers can comply with such tight constraints, NoCs feature many compelling properties. Should system requirements increase, more bandwidth can be easily added to a network. Physical design is made easier by the possibility of optimizing wire utilization and enforcing strict wire segmentation. Designing complex interconnection systems becomes a more streamlined activity, since a single homogeneous architecture must be deployed and validated. At the same time, very heterogeneous IP cores (in terms of data width, operating frequency, transaction types) can be plugged to a NoC, given the proper network adapters. The NoC itself can be shaped into arbitrary topologies to optimally match the communication needs of the cores; this is key to simultaneously satisfying application requirements and cost constraints. Generally speaking, NoCs feature more degrees of freedom than alternative architectures, which is a definite advantage in the highly heterogeneous SoC market. As can be seen, each design alternative for the interconnect fabric is very suitable for a subset of the SoC application space, but is limited in some other respect. Buses are cheap to manufacture, but

Figure 1.2: A general view of a NoC

have a clear performance scalability issue. Crossbars have the highest possible performance for medium-sized designs, however cost and wire routing issues also prevent scalability beyond a certain threshold. Hierarchical buses and mixed topologies struggle to provide the best tradeoff among performance and overheads in big designs, but also encounter a stumbling block in terms of complexity of design and validation. NoCs offer virtually unlimited scalability and a high potential for customization, but their implementation overhead has to be fully assessed first. The activities presented in this thesis aim to validate this claim with exhaustive design experiments.

# 1.6 Network-on-chip architectures features and classification

The efficiency of an interconnect architecture is evaluated taking into account its capability of supporting the system feasibility and communication requirements using some corresponding metrics.

A communication process is an information (data) transfer from an initiator unit (or masters) and one target unit (or slaves). The transfer can be "pushed" if the sending unit is an initiator or "pulled" when it is required by a target. The "protocol" specifies how data should be transfered from senders

to receivers. Some control information must also be provided to initiate a transfer, including for exemple an identifier of the destination. The "communication architecture" is devoted to implements the communication process. Every communication architecture, and thus every NoC, basically consists in:

- links: A "link" is a logical connection between two (or more) communication architecture components, is composed out of one or more physical communication channels supporting the signal carrying the information. Typically, on-chip networks communication channels, are physically implemented as global wires in current CMOS technologies.

- switching elements: A switching element is a component that connects its input ports with its output ports in a flexible manner, performing or not a connection between two links connected to it. Physically, while it is typically a multiplexer in a bus or a switching fabric in a crossbar based design, it consists in the switch of router in a Network-on-Chip.

- buffers: inside the communication architecture some storage resources are used to assure loss less communication and reduce cogestion.

Moreover, communication architectures in general, but especially NoCs, can require a *Network Interface*, that is a module devoted to perform a protocol conversion, from the protocol supported by the external environment, to the one featured by the communication infrastructure. In case of packet switched NoCs, the Network Interface (NI) is also in charge of packeting operations.

# 1.6.1 Network design constraints

Communication architecture design is performed taking into account several requirements posed by the system-level constraints:

#### • Connectivity requirements:

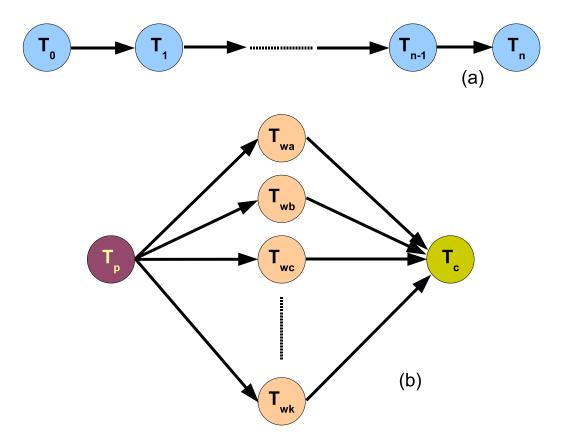

For a given application, the traffic pattern exposes the communication requirements between the different tasks. Any application can be described as a Control and Data Flow Graph (CDFG). The nodes of the graph represent the tasks, the edges represent the control and data dependencies. A control dependency implies that a task has to be completed before the next one can start. A data dependency represents data transfers between tasks. The application mapping can thus be viewed as the mapping of the CDFG on an architecture.

#### • Performance requirements:

can be evaluated using several metrics: the end-to-end network latency, defined as the delay between the injection of a data in the network at the source and its reception at the destination, that is only related to the network feaures; the end-to-end communication architecture latency, defined as the delay between the time the initiator starts its message transmission and the time the target receives the message, that includes the network interfaces latency; the set-up time, defined as the delay between the time at which control information is sent and the time at which data can be injected in the network; the throughput (or aggregated bandwidth), defined as the maximum amount of information per unit of time that the network can physically handle; the bisection bandwidth, defined as the sum of the bandwidths corresponding to the links intercepted by a cut which spans the least possible amount of edges (i.e. a min-cut) and partitions the network in two equal size parts.

#### • Performance guarantees:

Communication architecture performances are generally not predictable due to the contention when network resources can be shared among different users. However, real-time applications may have to meet strict temporal deadlines or require a minimum amount of bandwidth to operate properly. Multimedia applications generally contains many real-time data streams of different latency and bandwidth requirements.

#### • Scalability:

The scalability of a network is its aptitude to scale efficiently performance parameters and physical parameters in function of the number of communicating devices. In particular, the network aggregated bandwidth should increase proportionally when additional communicating devices are added to the network. The bandwidth per node can thus be preserved when additional nodes are connected.

#### • Physical constraints:

Physical constraints include wiring length, area overhead introduced by the communication architecture and energy and power consumption. Energy consumption should be limited to increase the battery lifetime, while power consumption should be minimized to restrain the chip temperature because advanced packaging and cooling systems are unaffordable for cheap embedded systems.

#### • Reliability and yield:

Besides providing performance guarantees during normal cases, a communication architecture will also have to provide mechanisms to tolerate exceptional circumstances that can alter network behavior. Basic metrics to mesure reliability are:

- Availability: measure of the probability that the network will remain operational

- Probability of failure on demand: measure of the probability of the network to behave in an unexpected way for a given request

- Rate of failure occurrence: measure of the network failure frequency on a given duration

- Mean Time To Failure (MTTF): measure of the mean time during which the network remains operational before a failure occurs.

A global network design cost function can then be built based on those soft and hard constraints. The design of the network will thus result from a trade-off between the satisfaction of those different parameters.

# 1.7 Network-on-chip architecture design space

The Network-on-chip communication architecture design space is extremely vast. Many network parameters can be set to tailor an optimal on-chip architecture. This section gives a brief summary of the principal network decisions.

## 1.7.1 Fundamental network parameters

#### Topology

The network topology defines the logical connections between switching elements and between the switching elements and the nodes. It can be represented by a graph G(C,N), the graph edges C being the connections between nodes and the vertices N being the nodes and switching elements of the network. The network topology is one of the most critical decision in on-chip communication architecture. It has a considerable impact on the network design costs. Topologies can be classified according to their features:

#### • direct-indirect

In direct networks, each switching device (e.g. router, switch) is connected to at least one communicating device (e.g. IP core). In indirect networks, a switching device is not necessarily connected to a

communicating device. It can be connected to other switching devices. Switching devices are connected with each other by point-to-point links. Hybrid networks is a mix of those two types of network.

#### • orthogonality

Most direct networks have an orthogonal topology. It means that nodes can be arranged in an orthogonal n-dimension space and that every link can be arranged in such a way that it provides a displacement in a single dimension. Strictly orthogonal topologies is a subset of orthogonal topologies for which every node has at least one link crossing each dimension.

#### • diameter

The diameter of a network topology is the maximum number of edges between a pair of vertices in the topology. The diameter can be linear, logarithmic or fixed line lengtht, depending on how diameter progresses increasing the number of nodes interconnected in the network.

#### • regularity

Topologies are said to be regular when all the vertices of the graph have the same number of edges connected to each vertex.

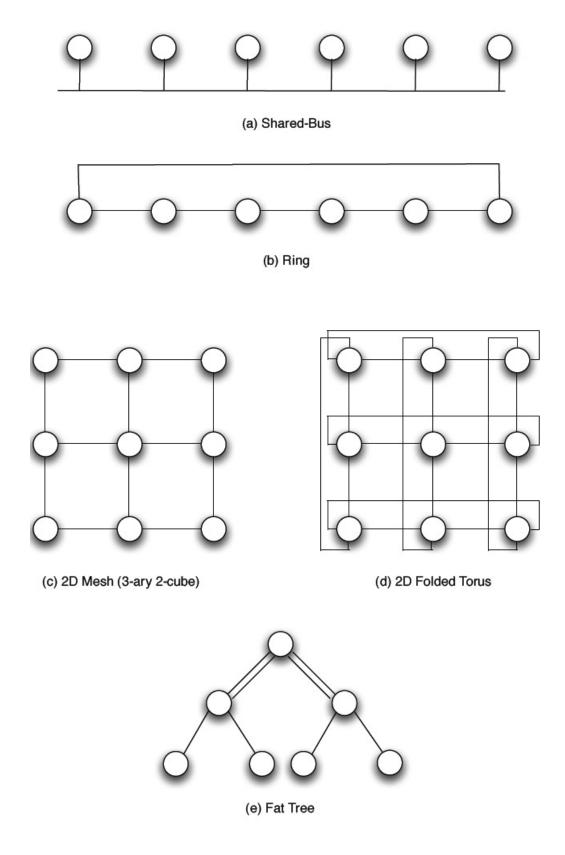

• general purpose-domain specific General purpose topologies are not optimized for a specific pattern. Examples are typically the mesh topology and k-ary n-cube networks in general. Traffic pattern specific topologies examples exploit traffic pattern knowledge, facilitate communication locality. An example of regular topology that is not general purpose is given by the fat-tree topology (see figure 1.3. This topology is regular but it exploits locality of traffic. On the other hand, it performs very badly with general purpose traffic as the root nodes will become a bottleneck.

Examples of topologies are shown in figure 1.3

#### Routing Technique

The routing technique decision consists in defining and implementing a strategy to choose one path from source to destination nodes when the topology offer multiple paths. In shared-buses, no routing technique is needed, since source and destination directly share the same medium. For hierarchical buses and bridged buses, there is only one path is available from source to destination. It is only needed to specify which bridges have to be switched. Routing algorithms can be classified according to several criteria:

Figure 1.3: Examples of common network topologies

#### • Number of destinations

If a message can be routed to multiple destinations at the same time, the routing technique will be classified as multicast (or broadcast for all possible destinations). If only one destination can be reached, it is said to be unicast. This choice mainly depends on the application requirements.

#### • Routing decision time

Routing decisions can be performed exclusively at run-time, exclusively at design-time or partly at design-time, partly at run-time.

#### • Routing decision locality

Locality of the routing decision: central/distributed/hybrid

#### • Locality of the routing technique implementation

The routing decisions can be performed by a central control unit (centralized routing) running one or several routine or along the network (distributed routing). Hybrid schemes are also possible. The particular case in which a centralized routing implementation is located at the source network interface is commonly referred to as source routing.

#### • Locality of the network status information

Information on the network status can be obtained at local ,global or semi-global level, or can not be taken into account at all (oblivious routing).

#### • Routing adaptivity

The routing strategy can be deterministic (fast and well adapted to be implemented in hardware), meaning that the routing decision is invariant for a given source and destination, or it can be adaptive, providing different routes depending on the network load (offering better performance and fault-tolerance).

#### • Number of paths

The routing algorithm can either consider all the paths offered by the topology from source to destination (complete routing algorithm) or only a sub-set of available paths (partial routing algorithm).

#### • Parallelization

The routing algorithm can be implemented by one sequential process or by multiple parallel processes executed on different processing cores. • Implementation

The routing decisions can be implemented in hardware(faster), software(more flexible) or in a combination of both.

#### Routing granularity

The routing granularity decision consists in defining at which data granularity the routing decision will be performed: circuit-based routing or packetbased routing. For a circuit-based routing technique, the routing decision is performed once for all at the establishment of the circuit. All the data will then transit through the same path offering predictable Quality of Service to that connection, once an extra-delay required at the circuit set-up time is payed. For a packet-based routing technique, the routing decision can be performed at the granularity of a packet. A packet is typically composed of a header containing routing informations and a payload which contains the data. Packet-size is an important parameter for the network. In the packet-based routing technique there is no circuit set-up delay and bandwidth utilization is closer to the optimum, no guarantees on available bandwidth and latency can be provided.

#### Flow Control Mechanism

The flow control defines the policy used to adjust the data flow between communicating devices. Data sending, generally, requires multiple transmissions since links bit-width is limited. The flow control can be performed at several levels and it defines the granularity at which data are sent through communication devices. Flow/congestion control strategies handles the transmission of data from a communication device input port to an output port. The communication device can be a switch or a bus.

#### Switching Technique

When applied to networks, different combinations of parameters such flow control granularity, or buffering placement corresponds to well-known switching techniques such as:

• real circuit switching

Real circuit switching consists of reserving a path across the network

from source to destination, typically sending an header over the network

from the source node. The header reserves the channels along the path.

When the probe arrives at the destination, a message is sent back to

confirm that the circuit has been established and proper data sending

can start. This switching technique is well suited for frequent and long messages between two nodes.

#### • store and forward

In SAF the messages is split in smaller independently routed chunks called packets. This scheme does not require full path pre-establishment overhead. Each packet is entirely stored in a buffer and only then can be forwarded to the next router.

#### • virtual cut through

VCT reduces the latency of SAF switching scheme. The switching granularity is smaller than a packet. Elements of the packet called flits can already be sent even if the packet is not fully arrived. If the packet's output port is busy, the packet is stored in a buffer. Buffer space is the same as for SAF.

#### • wormhole

In wormhole, the input buffer space is typically dimensioned to the size of a couple of flits. When a packet accesses a router output port used by another packet, the packet remains distributed over all the previous router buffers along the path.

#### • mad postman

The mad postman switching technique is comparable to the wormhole switching technique. The difference is that the flow granularity is set at the bit-level instead of the flit-level to reduce latency overhead.

#### • switched virtual circuit

In Switched Virtual Circuit an header is sent first. When it reaches the destination, an acknowledgment is sent back to the source The switched virtual circuit technique is appropriate for frequent and long messages.

The switching technique specify the way a message is forwarded on the network and considerably affects the network delay.

# 1.7.2 Network Design Decisions

On-chip communication architectures offer a vast design space. Designing a complete network thus appears as a very complex and difficult problem. It consists in performing decisions on the value of each parameter, to optimize a cost function. Real design decisions are generally neither completely independent nor fully dependent of each others. The on-chip communication architecture characteristics can be split following the OSI stack model in

which networks can be viewed at different abstraction layers. Upper layers decisions will impose constraints on the lower layers values of decisions to optimize a given cost function. As mentioned the seven layers of the OSI network model can be identified in an on-chip communication architecture: application, presentation, transport, network, link and physical layers.

The Application layer offers high-level communication services to the Intellectual Property (IP) cores. Application layer decisions are related to the definition of the inter-process communication interface and primitives (interfaces can be custom or compliant to widely diffused standard like Open Core Protocol) and to the supporting of a determined level of Quality of Service (QoS).

The *Presentation layer* provides data formatting services to the application layer (e.g. encryption).

The Session layer is managing the establishment and coordination of the end-to-end connections.

The presentation layer and the session layer are often merged with the neightbour layers in network protocol implementations.

The Transport layer offers services like end-to-end communication services to the IP cores. With respect to the transport layer, a decision must be taken between two modes of communication: the connection-oriented or connectionless modes. In the connection-oriented mode, after negotiation, source and destination agree on a set of QoS parameters. The end-to-end connection will act as if cores were directly interconnected to each other, and it must be established prior to the actual data transfer and released once it is no more exploited. In the connection-less mode the transport layer then simply forward data to the network layer after packetization. Moreover while defining the transport layer a decision must be taken on the flow and congestion control strategies used to prevent contention in the network either by adapting the source data flow to the network capacity or by adapting the flow of data transiting in the network. The most popular techniques are credit-based flow control and thresholdbased control. The credit-based flow control technique consists in permitting the incoming data to enter the network only when it acquires one flow control credit, that is released when the data arrive at the destination. The network load is limited by a fized number of credits allowed through the network. The threshold-based flow control is based on the regulation of data injection in the network depending on the network congestion status.

The *Network layer* describes how data are sent from source to destination node. It includes decisions about network topology, routing techniques and routing granularity.

The Link layer describes how data are sent between the communication de-

vices constituting the on-chip architecture. Decision taken at this layer are related to the encoding techniques, the switching techniques, the amount and the location of the buffering resources in the network, the arbitration techniques used to handle multiple access to a shared resource, the flow control granularity.

The *Physical layer* deals with the physical implementation of the network on the chip. It includes the circuit and process technologies that are used and the network physical lay-out. Synchronicity is also addressed in this layer as well as low-swing drivers and other interconnect options.

## 1.8 State of the Art NoC Architectures

This paragraph provides a big picture of the state of the art in NoC propositions, as currently found in the available literature, summarized in figure 1.4.

(NA or shadowed boxes means that data are not available, whereas GT means guaranteed throughput)

The features presented for each considered Data can be divided into three groups:

- features related to network and switch structure, presented in the four first columns;

- features related to performance data, in the following three columns;

- features related to prototyping and/or silicon implementation data, in the last column.

A basic common choice is the use of packet switching (with the exception of aSOC), where the definition of the route is fixed during the hardware instantiation time.

Two connected concepts, network topology and routing strategy, are the subject of the first column. The predominant network topology is the 2D mesh, because this choice implies three advantages:

- facilitated implementation using current IC planar technologies;

- simplicity of the XY routing strategy; and finally

- network scalability.

| NoC                 | Topology /<br>Routing                                                    | Flit Size                                                     | Buffering                                                                    | IP-<br>switch<br>Interface                  | Switch Area                                                                    | Estimated<br>Peak<br>Performance                            | QoS<br>Support                                        | Implementat<br>ion                                |

|---------------------|--------------------------------------------------------------------------|---------------------------------------------------------------|------------------------------------------------------------------------------|---------------------------------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------|---------------------------------------------------|

| SPIN - 2000         | Fat-tree /<br>Deterministic<br>and adaptive                              | 32 bits data<br>+ 4 bits<br>control                           | Input queue<br>+ 2 shared<br>output queue                                    | VCI                                         | 0.24 mm <sup>2</sup><br>CMOS 0.13μm                                            | 2 Gbits/s per<br>switch                                     |                                                       | ASIC layout<br>4.6 mm <sup>2</sup><br>CMOS 0.13μm |

| aSOC - 2000         | 2D mesh<br>(scalable) /<br>Determined by<br>application                  | 32 bits                                                       | None                                                                         |                                             | 50,000<br>transistors                                                          |                                                             | Circuit-<br>switching (no<br>wormhole)                | ASIC layout<br>CMOS 0.35µm                        |

| Dally - 2001        | Folded 2D torus<br>/ XY source                                           | 256 bits<br>data + 38<br>bits control                         | Input queue                                                                  |                                             | 0.59 mm <sup>2</sup><br>CMOS 0.1μm<br>(6.6 % of a tile)                        | 4 Gbits/s per<br>wire                                       | GT - virtual channels                                 | No                                                |

| Nostrum –<br>2001   | 2D mesh<br>(scalable) / Hot<br>potato                                    | 128 bits<br>data + 10<br>bits control                         | Input and output queues                                                      |                                             | 0.01 mm <sup>2</sup><br>CMOS 65nm                                              |                                                             |                                                       |                                                   |

| Sgroi - 2001        | 2D mesh / NA                                                             | 18 bits data<br>+ 2 bits<br>control                           |                                                                              | OCP                                         |                                                                                |                                                             |                                                       |                                                   |

| Octagon-<br>2001    | Chordal ring /<br>Distributed<br>and adaptive                            | Variable<br>data + 3 bits<br>control                          |                                                                              |                                             |                                                                                | 40 Gbits/s                                                  | Circuit-<br>switching                                 | No                                                |

| Marescaux -<br>2002 | 2D torus<br>(scalable) / XY<br>blocking, hop-<br>based,<br>deterministic | 16 bits data<br>+ 3 bits<br>control                           | Input queue                                                                  | Custom                                      | 611 slices<br>VirtexII (6.58%<br>area overhead<br>XC2V6000)                    | 320Mbits/s per<br>virtual channel<br>at 40 MHz              | 2 virtual<br>channels (to<br>avoid<br>deadlock)       | FPGA VirtexII /<br>VirtexII Pro                   |

| Bartic –<br>2003    | Arbitrary (parameterizable links) / Deterministic, virtual-cut- through  | Variable<br>data<br>+ 2 bits<br>control / link                | Output queue                                                                 | Custom                                      | 552 slices + 5<br>BRAMs VirtexII<br>Pro for 5<br>bidirectional<br>links router | 800Mbits/s per<br>channel for 16-<br>bit flits at 50<br>MHz | Injection rate<br>control,<br>congestion<br>control   | FPGA VirtexII<br>Pro                              |

| Æthereal -<br>2002  | 2D mesh /<br>Source                                                      | 32 bits                                                       | Input queue                                                                  | DTL<br>(Philips<br>proprietary<br>standard) | 0.26 mm <sup>2</sup><br>CMOS 0.12μm                                            | 80Gbits/s per<br>switch                                     | Circuit-<br>switching                                 | ASIC layout                                       |

| Eclipse –<br>2002   | 2D sparse<br>hierarchical<br>mesh / NA                                   | 68 bits                                                       | Output queue                                                                 |                                             |                                                                                |                                                             |                                                       | No                                                |

| Proteo –<br>2002    | Bi-directional<br>ring / NA                                              | Variable control and data sizes                               | Input and output queues                                                      | VCI                                         |                                                                                |                                                             |                                                       | ASIC layout<br>CMOS 0.18µm                        |

| SOCIN -<br>2002     | 2D mesh<br>(scalable) / XY<br>source                                     | n bits data +<br>4 bits control<br>(parameteriz<br>able)      | Input queue<br>(parameteriza-<br>ble)                                        | VCI                                         | 420 LCs APEX<br>FPGAs<br>(Estimated, for<br>n=8, bufferless)                   | 1 Gbits/s per<br>switch at 25<br>MHz                        | No                                                    | No                                                |

| SoCBus –<br>2002    | 2D mesh / XY<br>adaptive                                                 | 16 bits data<br>+ 3 bits<br>control                           | Single position<br>input and<br>output buffers                               | Custom                                      |                                                                                | 2.4 Gbits/s per<br>link                                     | Circuit-<br>switching                                 | No                                                |

| QNOC - 2003         | 2D mesh regular<br>or irregular / XY                                     | 16 bits data<br>+ 10 bits<br>control<br>(parameteriz<br>able) | Input queue<br>(parameterize-<br>ble) + Output<br>queue (single<br>position) | Custom                                      | 0.02 mm <sup>2</sup><br>CMOS 90nm<br>(Estimated)                               | 80 Gbits/s per<br>switch for 16-bit<br>flits at 1GHz        | GT - virtual<br>channels, (4<br>different<br>traffic) | No                                                |

| T-SoC –<br>2003     | Fat-tree /<br>Adaptive                                                   | 38 bits<br>maximum                                            | Input and output queues                                                      | Custom/<br>OCP                              | 27000 to 36000<br>two input NAND<br>gates                                      |                                                             | GT - 4 virtual channels                               |                                                   |

| Xpipes –<br>2002    | Arbitrary (design<br>time) / Source<br>static (street<br>sign)           | 32, 64 or<br>128 bits                                         | Virtual output<br>queue                                                      | ОСР                                         | 0.33 mm <sup>2</sup><br>CMOS 100nm<br>(Estimated)                              | 64 Gbits/s per<br>switch for 32-bit<br>flits at 500MHz      | No                                                    | No                                                |

| Hermes –<br>2003    | 2D mesh<br>(scalable) / XY                                               | 8 bits data +<br>2 bits control<br>(parameteriz<br>able)      | Input queue<br>(parameteriza-<br>ble)                                        | ОСР                                         | 555 LUTs<br>278 slices<br>VirtexII                                             | 500 Mbits/s per<br>switch at 25<br>MHz                      | No                                                    | FPGA<br>VirtexII                                  |

Figure 1.4: State of the art in NoCs overview

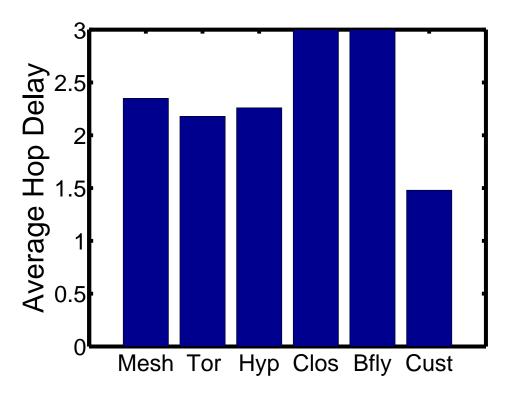

Another approach is to use the 2D torus topology, to reduce network diameter (Marescaux-2002). The folded 2D torus (Dally-2001) reduces also the cost in wiring. A common problem of mesh and torus topologies is the associated network latency. To overcome this problem the following architectures have been proposed:

- SPIN that employ a fat-tree topology;

- T-SoC that employ a fat-tree topology; and finally

- Octagon that proposes the use of a chordal ring topology.

All of them lead to a smaller network diameter, with consequent latency reduction. Concerning routing strategies, there is a clear lack of published information; this means that this is still an open field.

The second important quantitative parameter of NoC switches is flit size. It is possible to classify approaches in two groups the first one focused on future SoC technologies and the other concerned on the existing limitations. The first group uses wide switching channels (150 to 300 wires), without significantly affecting the overall SoC area. This can be achieved by using a future 60nm technology for building 22mm x 22mm chip with a 10 x 10 NoC to connect 100 2mm x 2mm IPs. The second group uses flit size ranging mostly from 8 to 64 bits, a data width similar to current processor architectures. The next parameter considered is the switch buffering strategy. Most NoCs employ input queue buffers. Since input queuing implies a single queue per input, this leads to lower area overhead but, at the same time, presents problems of head-of-line blocking. To overcome this problem, output queuing can be used, the counterbalance of this improvement is a greater buffering cost, since the total number of queues is increases. An intermediate solution is to use virtual output queuing associated with time-multiplexed virtual channels ( $\times$ pipes).

Another important parameter, related to the buffering field, is the FIFO size, which implies the need to solve the compromise among of the amount of network contention, packet latency and switch area overhead. Bigger queues lead to small network contention, higher packet latency, and bigger switches; other way round for the smaller ones.

The last structural parameter is the characteristic of the IP-switch interface. The use of standard communication interfaces for the on-chip environment is an evolving trend in industry and academia, to allow re-use of cores. VCI and OCP standards are used by several of the NoC proposals presented in figure 1.4.

The fifth column collects results concerning the size of the switch. It is interesting to observe that the two approaches targeted to ASICs (SPIN-2000 and Æthereal-2002), both with a 32-bit flit size, have similar dimensions, around 0.25mm2 for similar technologies. FPGA prototyped systems produced results ranging from 555 LUTs (Hermes-2003) to 1222 LUTS (611 slices) (Marescaux-2002). This difference comes from the fact that Marescaux-2002 employs virtual channels, while Hermes-2003 does not, leading to smaller switch area. Switch size, flit size and switch port cardinality are fundamental values to allow estimating the area overhead and the expected peak performance for on-chip communication.

In the following, two communication architectures, a bus based and a NoC, are presented more in detail, being the reference for the discussions reported in following chapters.

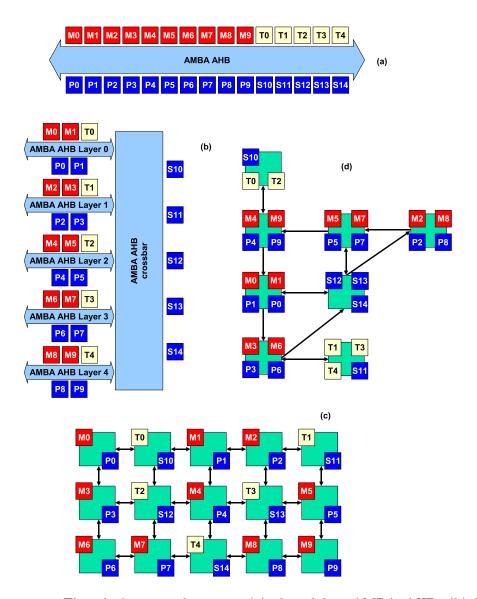

#### 1.8.1 AMBA Shared Bus

The Advanced Microcontroller Bus Architecture (AMBA) 2.0 [4] interconnect is a well-established fabric architecture for SoC designs, thanks to its efficiency despite the moderate silicon footprint. Therefore, we choose it as a reference against which to compare the ×pipes NoC. The AMBA specification dictates three different architectures with varying levels of complexity and performance; in this paper, we will refer to Advanced High-performance Bus (AMBA AHB), the fastest of them.

AMBA traditionally leverages upon a shared bus topology, and its communication protocol is kept simple to minimize area overhead (a single ongoing transaction at a time, no posted writes, etc.). An AHB bus is composed of several IP blocks (AHB masters and slaves), of one central arbiter to manage resource access, and of some interconnection resources. A minimal amount of flip-flops is required in the architecture, which is typically bufferless. The bus resources are owned by a single master at a time; if the targeted slave is forced to insert wait states before responding, no other transaction can be initiated, neither by the current bus owner nor by any other master. As a result, the utilization of bus bandwidth, which is already limited, might be poor.

AMBA AHB uses non-pipelined paths for communication among all masters and all slaves. Therefore, a key performance assumption is that the propagation delay of the interconnect wires will be short. If that is the case, communication will incur the minimum possible latency. However, new technology nodes are leading to faster and faster logic, potentially resulting in faster clock periods, while wire propagation delays are proportionally increasing. If the whole fabric is constrained to slow operation by wire delay, this

factor represents a limit to maximum operating frequency.

## 1.8.2 AMBA Multi-Layer

Due to increasing congestion and bandwidth demands in modern SoCs, a crossbar component was added to the AMBA toolkit, resulting in "Multi-Layer" (ML) AMBA designs. To keep existing AMBA interfaces unchanged, the device is purely combinational and completely transparent to AMBA masters and slaves. The crossbar component behaves as a slave towards multiple AMBA AHB buses ("layers"), and forwards requests to real AMBA slaves (e.g. memories). Multiple layers can simultaneously access the crossbar, provided they do not conflict on arbitration for the same transaction target.

Given its high-bandwidth topological nature and its combinational response times, this crossbar is clearly a best-case reference block from an architectural point of view. However, from the perspective of a layout engineer, wire routing constraints in such a block are very demanding. Therefore, an assessment of the achievable clock frequency and area is clearly essential.

#### 1.8.3 ×pipes NoC

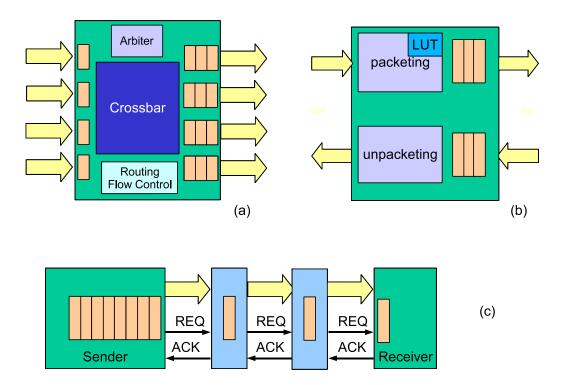

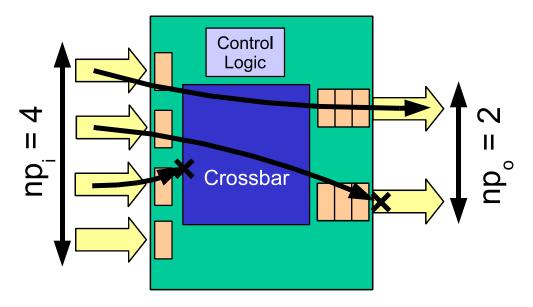

The ×pipes NoC [3, 15] is an example of a highly flexible library of component blocks (Fig. 1.5). The NoC is instantiated by deploying a set of components in an arbitrary topology and by configuring them. The ×pipes library contains three main components: switches, Network Interfaces (NIs) and links.

The backbone of the NoC is composed of switches, whose main function is to route packets from sources to destinations. Arbitrary switch connectivity is possible, allowing for implementation of any topology. Switches provide buffering resources to lower congestion and improve performance; in  $\times$ pipes , output buffering is chosen, *i.e.* FIFOs are present on each output port. Switches also handle flow control [13] issues (we use the ACK/NACK protocol in this paper), and resolve conflicts among packets when they overlap in requesting access to the same physical links.

An NI is needed to connect each IP core to the NoC. NIs convert transaction requests/responses into packets and vice versa. Packets are then split into a sequence of flits before transmission, to decrease the physical wire parallelism requirements. In ×pipes, two separate NIs are defined, an *initiator* and a *target* one, respectively associated to system masters and system slaves. A master/slave device will require an NI of each type to be attached to it. The interface among IP cores and NIs is point-to-point as defined by the OCP 2.0 [12] specification, guaranteeing maximum reusability. NI Look-Up

Figure 1.5: ×pipes building blocks: (a) switch, (b) NI, (c) link

Tables (LUTs) specify the path that packets will follow in the network to reach their destination (source routing). Two different clock signals can be attached to NIs: one to drive the NI front-end (OCP interface), the other to drive the NI back-end (×pipes interface). The ×pipes clock frequency must be an integer multiple of the OCP one. This arrangement allows the NoC to run at a fast clock even though some or all of the attached IP cores are slower, which is crucial to keep transaction latency low. Since each IP core can run at a different divider of the ×pipes frequency, mixed-clock platforms are possible.

Inter-block links are a critical component of NoCs, given the technology trends for global wires. The problem of signal propagation delay is, or will soon become, critical. For this reason, ×pipes supports link pipelining [13], i.e. the interleaving of logical buffers along links. Proper flow control protocols are implemented in link transmitters and receivers (NIs and switches) to make the link latency transparent to the surrounding logic. Therefore, the overall platform can run at a fast clock frequency, without the longest wires being a global speed limiter. Only the links which are too long for single-cycle propagation will need to pay a repeater latency penalty.

# Bibliography

- [1] International technology roadmap for semiconductors (ITRS). Technical report, International Technology Roadmap for Semiconductors.

- [2] Tapani Ahonen et al. A brunch from the coffee table case study in NoC platform design. In J. Nurmi, H. Tenhunen, J. Isoaho, and A. Jantsch, editors, Interconnect-Centric Design for Advanced SoC and NoC, pages 425-453. Kluwer Academic Publishers, 2004.

- [3] Federico Angiolini, Paolo Meloni, Davide Bertozzi, Luca Benini, Salvatore Carta, and Luigi Raffo. Networks on chips: A synthesis perspective. In Proceedings of the 2005 ParCo Conference (to be published), 2005.

- [4] ARM Ltd. The Advanced Microcontroller Bus Architecture (AMBA) homepage. www.arm.com/products/solutions/AMBAHomePage.html.

- [5] Luca Benini and Giovanni De Micheli. Networks on chips: A new SoC paradigm. *IEEE Computer*, 35(1):70 78, January 2002.

- [6] William J. Dally and Brian Towles. Route packets, not wires: On-chip interconnection networks. In Proceedings of the 38th Design Automation Conference, pages 684-689, June 2001.

- [7] Jorg Henkel, Wayne Wolf, and Srimat Chakradhar. On-chip networks: A scalable, communication-centric embedded system design paradigm. vlsid, 00:845, 2004.

- [8] M. Horowitz, R. Ho, and K. Mai. The future of wires, 1999.

- [9] Ali Keshavarzi, Kaushik Roy, and Charles F. Hawkins. Intrinsic leakage in deep submicron cmos ics-measurement-based test solutions. IEEE Trans. Very Large Scale Integr. Syst., 8(6):717-723, 2000.

- [10] Anthony Leroy. Optimizing the on-chip communication architecture of low power Systems-on-Chip in Deep Sub-Micron technology. PhD thesis, Universite Libre de Bruxelles Faculte des Sciences Appliquees, 2007.

- [11] James D. Meindl. Interconnect opportunities for gigascale integration. IEEE Micro, 23(3):28-35, 2003.

- [12] Open Core Protocol Specification, Release 2.0. www.ocpip.org, 2003.

- [13] Antonio Pullini, Federico Angiolini, Davide Bertozzi, and Luca Benini. Fault tolerance overhead in network-on-chip flow control schemes. In Proceedings of the 18th Annual Symposium on Integrated Circuits and System Design (SBCCI), pages 224-229, 2005.

- [14] Sonics Inc. SonicsMX. www.sonicsinc.com/sonics/products/smx/.

- [15] Stergios Stergiou, Federico Angiolini, Salvatore Carta, Luigi Raffo, Davide Bertozzi, and Giovanni De Micheli. ×pipes Lite: A synthesis oriented design library for networks on chips. In *Proceedings of the 2005 Design, Automation and Test in Europe Conference (DATE)*, pages 1188–1193. IEEE, 2005.

- [16] STMicroelectronics. The STBus interconnect. www.st.com.

- [17] Drew Wingard. Micronetwork-based integration for SoCs. In Proceedings of the 38th Design Automation Conference (DAC), pages 673–677. ACM, June 2001.

# Chapter 2

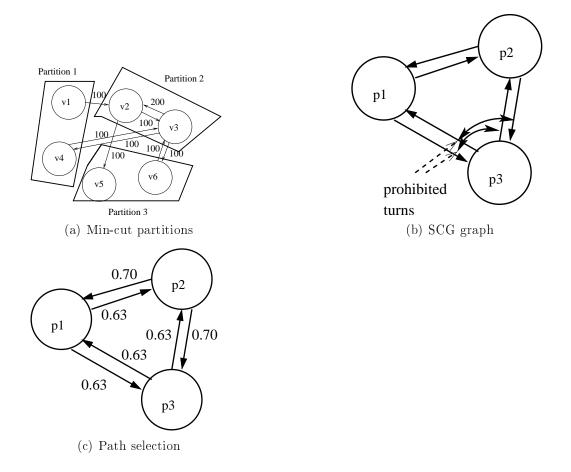

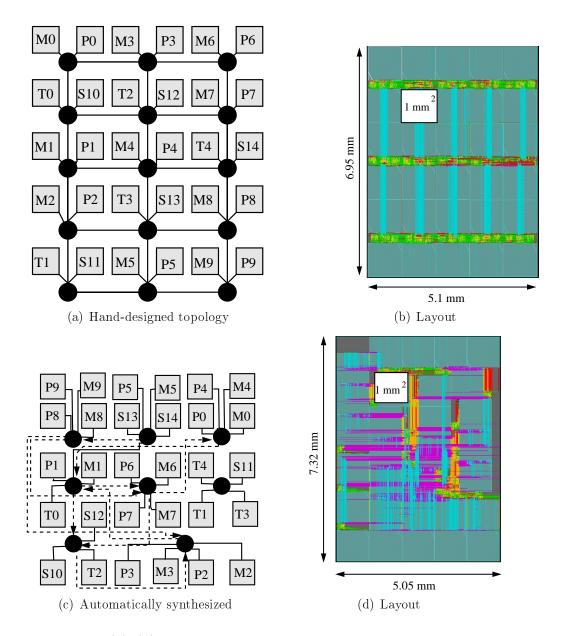

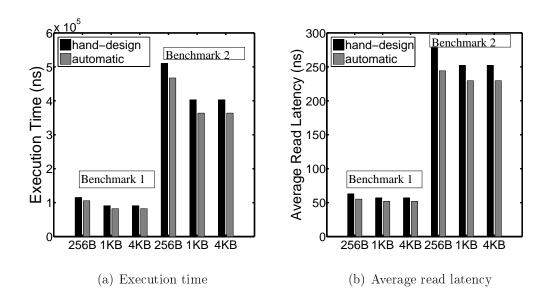

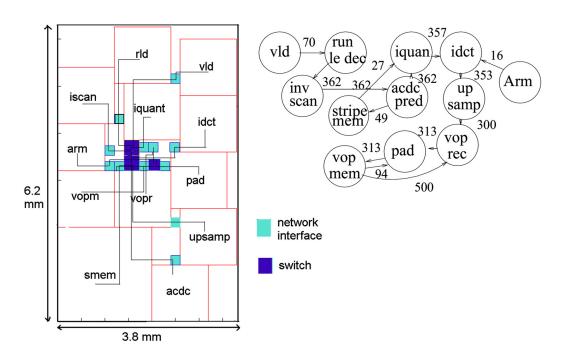

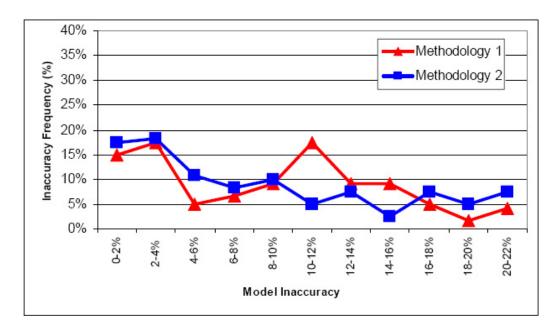

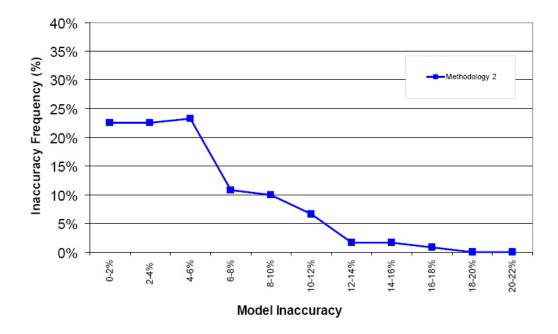

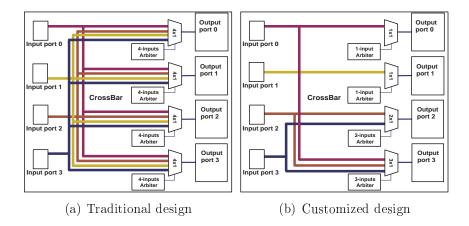

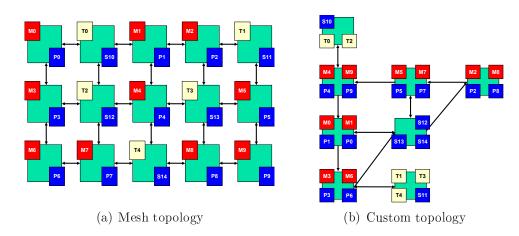

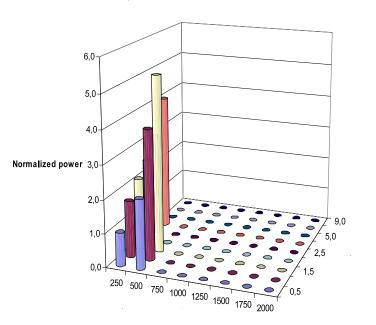

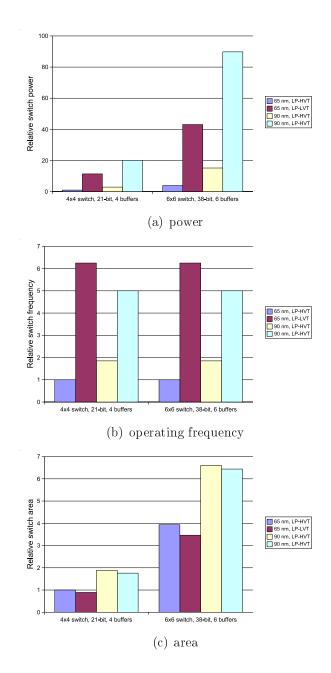

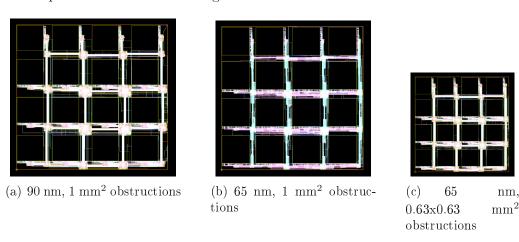

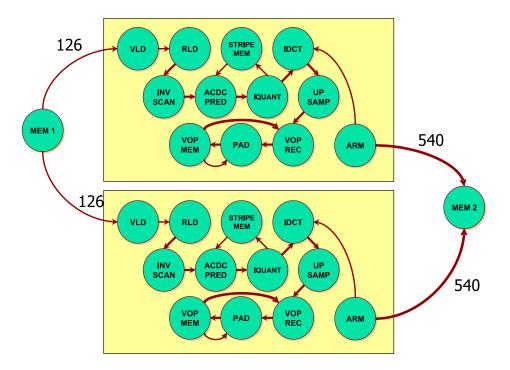

# Comparative analysis of NoCs and Traditional Interconnects